# ***Basic Structure of Computers***

## **&**

# ***Input/Output Organizations***

**TOPIC: Basic Structure of Computers:** Basic Operational Concepts, Bus Structures, Performance –Processor Clock, Basic Performance Equation, Clock Rate, Performance Measurement. **Machine Instructions and Program:** Memory Location and Addresses Memory Operations, Instructions and Instruction Sequencing, Addressing Modes, Assembly Language, Basic Input and Output Operations, Stacks and Queues, Subroutines, Additional Instructions, Encoding of Machine Instructions

## **1. BASIC OPERATIONAL CONCEPT:**

The program to be executed is stored in memory. Instructions are accessed from memory to the processor one by one and executed.

### **STEPS FOR INSTRUCTION EXECUTION**

Consider the following instruction

**Ex: 1 Add LOCA, R<sub>0</sub>**

This instruction is in the form of the following instruction format

**Opcode Source, Source/ Destination**

Where Add is the *operation code*, LOCA is the Memory operand and R<sub>0</sub> is Register operand. This instruction adds the contents of memory location LOCA with the contents of Register R<sub>0</sub> and the result is stored in R<sub>0</sub> Register.

The symbolic representation of this instruction is

**R<sub>0</sub> ← [LOCA] + [R<sub>0</sub>]**

The contents of memory location LOCA and Register R<sub>0</sub> before and after the execution of this instruction is as follows

Before instruction execution

**LOCA = 23H**

**R<sub>0</sub> = 22H**

After instruction execution

**LOCA = 23H**

**R<sub>0</sub> = 45H**

### **The steps for instruction execution are as follows**

1. Fetch the instruction from memory into the IR (instruction register in CPU).

2. Decode the instruction 1111000000 10011010

3. Access the first Operand

4. Access the second Operand

5. Perform the operation according to the Opcode (operation code).

6. Store the result into the Destination Memory location or Destination Register.

**Ex:2      Add R<sub>1</sub>, R<sub>2</sub>, R<sub>3</sub>    (3 address instruction format)**

This instruction is in the form of the following instruction format

Opcode, Source-1, Source-2, Destination

Where R1 is Source Operand-1, R2 is the Source Operand-2 and R3 is the Destination. This instruction adds the contents of Register R1 with the contents of R2 and the result is placed in R3 Register.

The symbolic representation of this instruction is

$$R3 \leftarrow [R1] + [R2]$$

The contents of Registers R1,R2,R3 before and after the execution of this instruction is as follows.

Before instruction execution

**R1 = 24H**

**R2 = 34H**

**R3 = 38H**

After instruction execution

**R1 = 24H**

**R2 = 34H**

**R3 = 58H**

**The steps for instruction execution is as follows**

1. Fetch the instruction from memory into the IR.

2. Decode the instruction

3. Access the First Operand R1

4. Access the Second Operand R2

5. Perform the operation according to the Operation Code.

6. Store the result into the Destination Register R3.

***CONNECTION BETWEEN MEMORY AND PROCESSOR***

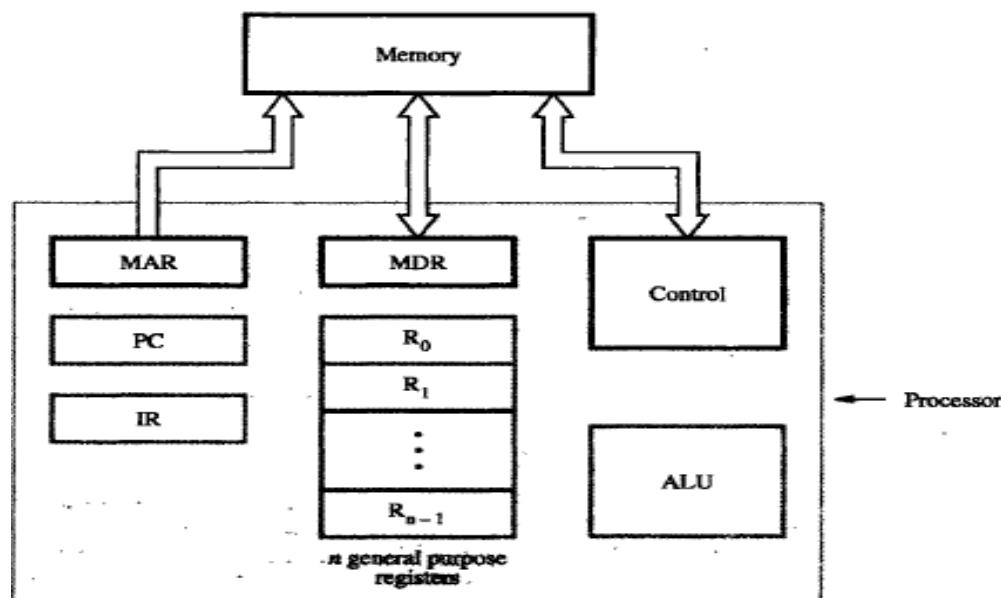

The connection between Memory and Processor is as shown in the figure.

The Processor consists of different types of registers.

1. MAR (Memory Address Register)

2. MDR (Memory Data Register)

3. Control Unit

4. PC (Program Counter)

5. General Purpose Registers

6. IR (Instruction Register)

7. ALU (Arithmetic and Logic Unit)

The functions of these registers are as follows

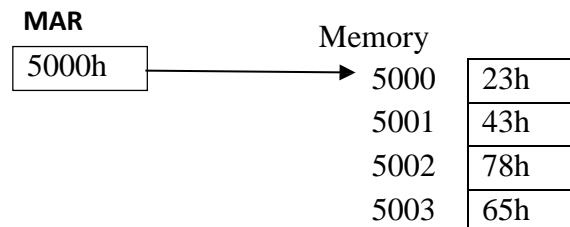

### 1. MAR

- It establishes communication between Memory and Processor

- It stores the address of the Memory Location as shown in the figure.

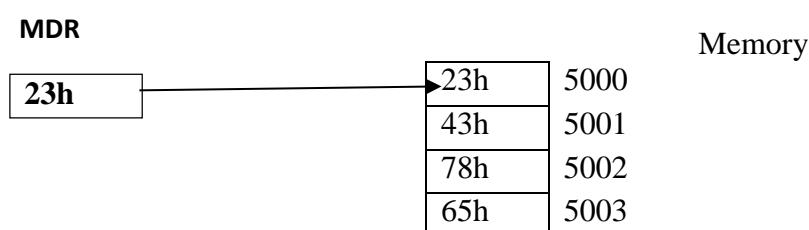

### 2. MDR

- It also establishes communication between Memory and the Processor.

- It stores the **contents** of the memory location (data or operand), written into or read from memory as shown in the figure.

### 3. CONTROL UNIT

- It controls the data transfer operations between memory and the processor.

- It controls the data transfer operations between I/O and processor.

- It generates control signals for Memory and I/O devices.

#### 4. PC (PROGRAM COUNTER)

- It is a special purpose register used to hold the address of the next instruction to be executed.

- The contents of PC are incremented by 1 or 2 or 4, during the execution of current instruction.

- The contents of PC are incremented by 1 for 8 bit CPU, 2 for 16 bit CPU and for 4 for 32 bit CPU.

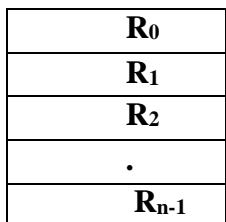

#### 4. GENERAL PURPOSE REGISTER / REGISTER ARRAY

The structure of register file is as shown in the figure

- It consists of set of registers.

- A register is defined as group of flip flops. Each flip flop is designed to store 1 bit of data.

- It is a storage element.

- It is used to store the data temporarily during the execution of the program(eg: result).

- It can be used as a pointer to Memory.

- The Register size depends on the processing speed of the CPU

- EX: Register size = 8 bits for 8 bit CPU

#### 5. IR (INSTRUCTION REGISTER)

It holds the instruction to be executed. It notifies the control unit, which generates timing signals that controls various operations in the execution of that instruction.

#### 6. ALU (ARITHMETIC and LOGIC UNIT)

- It performs arithmetic and logical operations on given data.

##### Steps for fetch the instruction

PC contents are transferred to MAR

Read signal is sent to memory by control unit.

The instruction from memory location is sent to MDR.

The content of MDR is moved to IR.

$$[\text{PC}] \rightarrow \text{MAR} \xrightarrow{\text{CU ( read signal) }} \text{Memory} \rightarrow \text{MDR} \rightarrow \text{IR}$$

## 2. BUS STRUCTURE

**Bus** is defined as set of parallel wires used for data communication between different parts of computer. Each wire carries 1 bit of data. There are 3 types of buses, namely

1. Address bus

2. Data bus and

3. Control bus1.

1. ***Address bus :***

- It is unidirectional.

- The processor (CPU) sends the address of an I/O device or Memory device by means of this bus.

2. ***Data bus***

- It is a bidirectional bus.

- The CPU sends data from Memory to CPU and vice versa as well as from I/O to CPU and vice versa by means of this bus.

3. ***Control bus:***

- This bus carries control signals for Memory and I/O devices. It generates control signals for Memory namely MEMRD and MEMWR and control signals for I/O devices namely IORD and IOWR.

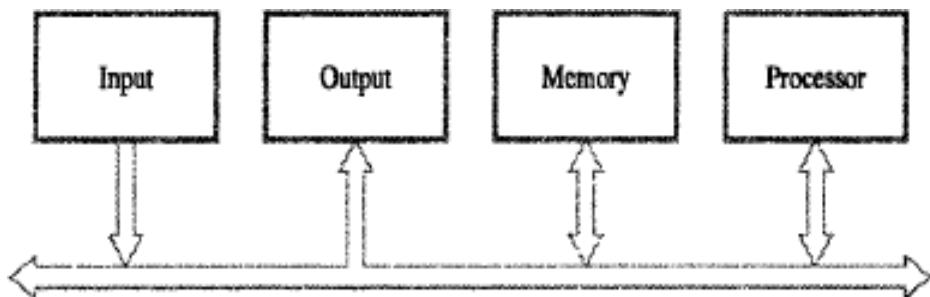

The structure of single bus organization is as shown in the figure.

- The I/O devices, Memory and CPU are connected to this bus is as shown in the figure.

- It establishes communication between two devices, at a time.

Features of Single bus organization are

- Less Expensive

- Flexible to connect I/O devices.

- Poor performance due to single bus.

There is a variation in the devices connected to this bus in terms of speed of operation. Few devices like keyboard, are very slow. Devices like optical disk are faster. Memory and processor are faster, but all these devices uses the same bus. Hence to provide the synchronization

between two devices, a buffer register is attached to each device. It holds the data temporarily during the data transfer between two devices.

### 3. PERFORMANCE

#### Basic performance Equation

- The performance of a Computer System is based on hardware design of the processor and the instruction set of the processors.

- To obtain high performance of computer system it is necessary to reduce the execution time of the processor.

- Execution time: It is defined as total time required executing one complete program.

- The processing time of a program includes time taken to read inputs, display outputs, system services, execution time etc.

- The performance of the processor is inversely proportional to execution time of the processor.

More performance = Less Execution time.

Less Performance = More Execution time.

The Performance of the Computer System is based on the following factors

1. *Cache Memory*

2. *Processor clock*

3. *Basic Performance Equation*

4. *Instructions*

5. *Compiler*

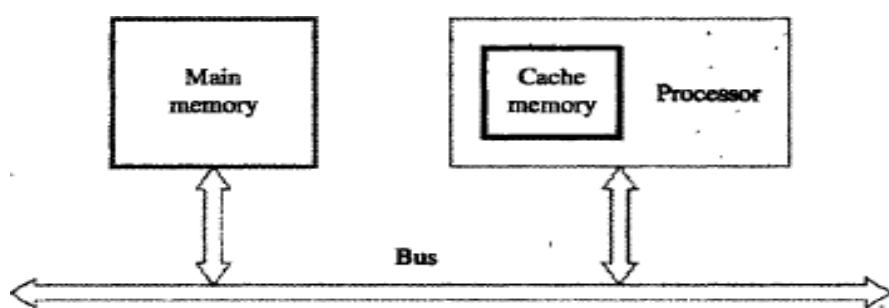

**CACHE MEMORY:** It is defined as a *fast access memory* located in between CPU and Memory. It is part of the processor as shown in the fig

The processor needs more time to read the data and instructions from main memory because main memory is away from the processor as shown in the figure. Hence it slowdown the performance of the system.

The processor needs less time to read the data and instructions from Cache Memory because it is part of the processor. Hence it improves the performance of the system.

**PROCESSOR CLOCK:** The processor circuits are controlled by timing signals called as Clock. It defines constant time intervals and are called as Clock Cycles. To execute one instruction there are 3 basic steps namely

1. Fetch

2. Decode

3. Execute.

The processor uses one clock cycle to perform one operation as shown in the figure

|               |       |        |         |

|---------------|-------|--------|---------|

| Clock Cycle → | T1    | T2     | T3      |

| Instruction → | Fetch | Decode | Execute |

The performance of the processor depends on the length of the clock cycle. To obtain high performance reduce the length of the clock cycle. Let ‘P’ be the number of clock cycles generated by the Processor and ‘R’ be the Clock rate .

The Clock rate is inversely proportional to the number of clock cycles.

$$\text{i.e } R = 1/P.$$

Cycles/second is measured in Hertz (Hz). Eg: 500MHz, 1.25GHz.

Two ways to increase the clock rate –

- Improve the IC technology by making the logical circuit work faster, so that the time taken for the basic steps reduces.

- Reduce the clock period, P.

### **BASIC PERFORMANCE EQUATION**

Let ‘T’ be *total time* required to execute the program.

Let ‘N’ be the *number of instructions* contained in the program.

Let ‘S’ be the *average number of steps* required to execute one instruction.

Let ‘R’ be number of clock cycles per second generated by the processor to execute one program.

Processor Execution Time is given by

$$T = N * S / R$$

This equation is called as Basic Performance Equation.

For the programmer the value of T is important. To obtain high performance it is necessary to reduce the values of N & S and increase the value of R

Performance of a computer can also be measured by using **benchmark** programs.

SPEC (System Performance Evaluation Corporation) is an non-profitable organization, that measures performance of computer using SPEC rating. The organization publishes the application programs and also time taken to execute these programs in standard systems.

$$SPEC = \frac{\text{Running time of reference Computer}}{\text{Running time of computer under test}}$$

### **DIFFERENCES MULTIPROCESSOR AND MULTICOMPUTER**

| <b>MULTIPROCESSOR</b>                                                | <b>MULTICOMPUTER</b>                                         |

|----------------------------------------------------------------------|--------------------------------------------------------------|

| 1. Interconnection of two or more processors by means of system bus. | Interconnection of two or more computers by means of cables. |

| 2. It uses common memory to hold the data and instructions.          | It has its own memory to store data and instructions.        |

| 3. Complexity in hardware design.                                    | Not much complexity in hardware design.                      |

| 4. Difficult to program for multiprocessor system.                   | Easy to program for multiprocessor system                    |

## **4. MEMORY LOCATIONS AND ADDRESSES**

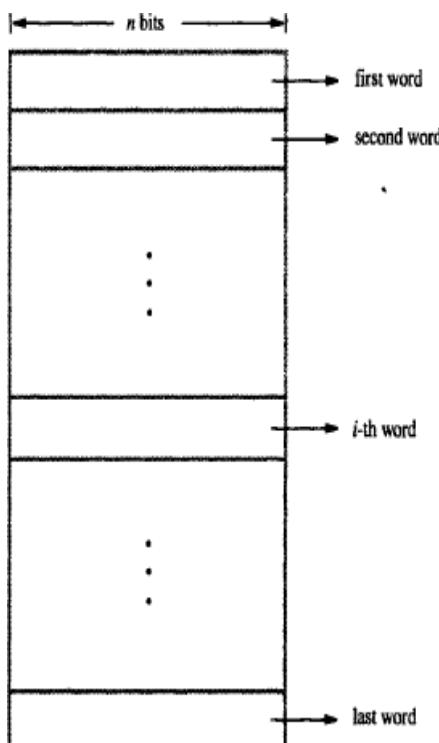

1. Memory is a storage device. It is used to store character operands, data operands and instructions.

2. It consists of number of semiconductor cells and each cell holds 1 bit of information. A group of 8 bits is called as byte and a group of 16 or 32 or 64 bits is called as word.

Word length = 16 for 16 bit CPU and Word length = 32 for 32 bit CPU. Word length is defined as number of bits in a word.

- Memory is organized in terms of bytes or words.

- The organization of memory for 32 bit processor is as shown in the fig.

The contents of memory location can be accessed for read and write operation. The memory is accessed either by specifying address of the memory location or by name of the memory location.