# DIGITAL ELECTRONICS

1.1

## MODULE 1: PRINCIPLES OF COMBINATION LOGIC

- Definition of combinational logic

- Canonical forms

- Generation of switching equations from Truth tables.

- Karnaugh Maps (3, 4 & 5 variables)

- Incompletely specified functions

- Simplifying Maxterm equations

- Quine Mccluskey minimization technique.

- Quine Mccluskey using don't care terms.

### Reduced Prime Implicants Tables.

III ECE

## DEFINITION OF COMBINATIONAL LOGIC

- combinational logic deals with the techniques of combining the basic gates into circuits that perform some desired function.

Ex: Adders, Subtractors, Decoders,

Encoders, Multipliers, Dividers,

Display drivers and Keyboard

Encoders.

- Logic circuit without feedback from output to the input, constructed from a functionally complete gate set, are said to be combinational.

- Logic circuits that contain no memory are combinational.

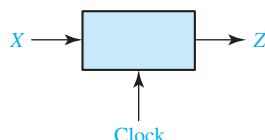

## COMBINATIONAL LOGIC MODEL.

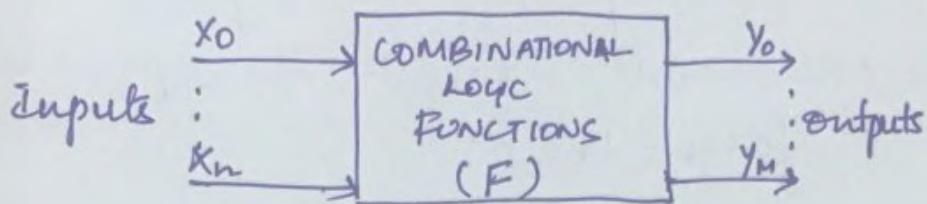

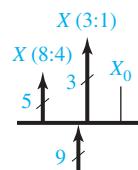

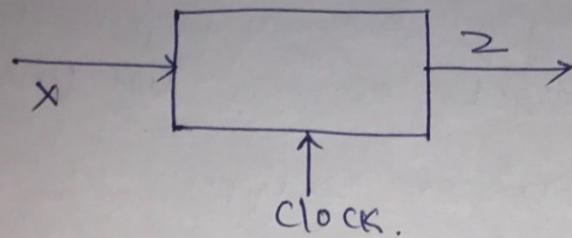

- Combinational logic <sup>can be</sup> modeled as shown in fig 1.1.

Fig 1.1 - COMBINATIONAL LOGIC MODEL

- Let  $\underline{x}$  be the set of all input variables  $\{x_0, x_1, \dots, x_n\}$  and  $\underline{y}$  be the set of all output variables  $\{y_0, y_1, \dots, y_m\}$ .

- The combinational function  $\underline{F}$ , operates on the input variable set  $\underline{x}$ , to produce the output variable set  $\underline{y}$ .

- Output Variables  $y_0$  through  $y_m$  are not fed back to the input. The output is related to input as

$$Y = F(x)$$

- The relationship between the input and output variables can be expressed in equations, logic diagrams or truth tables.

- A truth table specifies the input conditions under which the ops are true or false (1 or 0).

- Switching equations are then derived from the truth tables and realized using gates.

### PROBLEM STATEMENTS TO TRUTH TABLE

- Before any combinational logic system can be designed it must be defined.

- Proper statement of a problem is the most important part of any digital design task.

- Once correctly and clearly stated, any problem can be converted to the necessary logic for implementation.

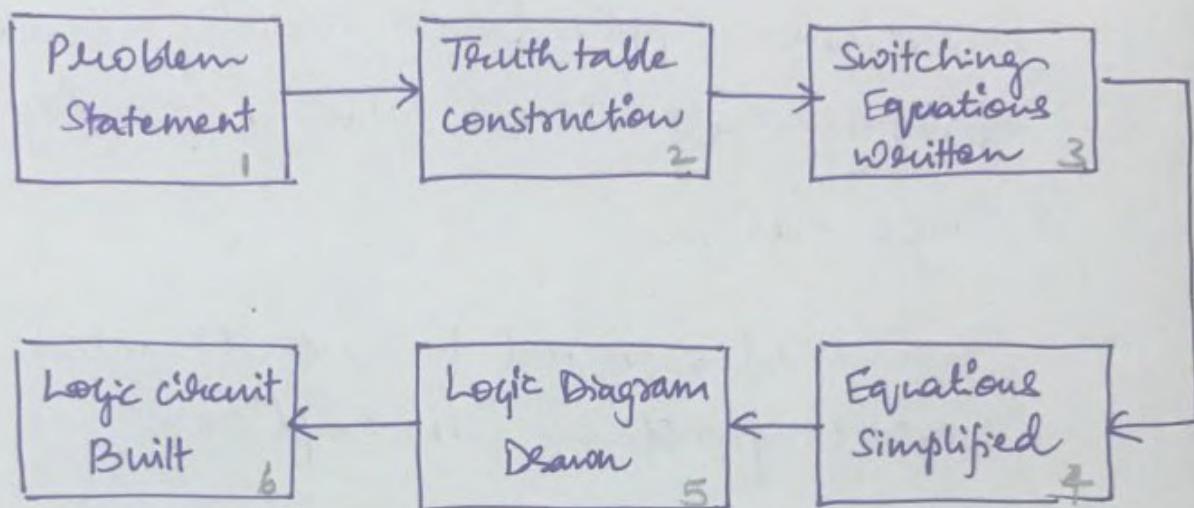

## GENERAL LOGIC DESIGN SEQUENCE

1.3

Fig 1.2 illustrates the sequence of design tasks in a general way.

Fig 1.2 - GENERAL LOGIC DESIGN SEQUENCE

1. First task is to define the Problem to be solved.

2. The problem is then rewritten in the form of a truth table.

- 3,4,5. From the truth table, the Switching equations can be written and simplified and the logic diagram drawn.

6. The logic diagram can be realized using any of the three main digital integrated circuit families.

TTL - Transistor - Transistor Logic

ECL - Emitter coupled logic or

CMOS - complementary Metal-oxide

Silicon.

- Practical applications rarely come in a prepackaged truth table, ready for logic design.

- Truthtables must be constructed from verbal problem descriptions.

Ex Pg 6, 7, 8, 9.

## DERIVING SWITCHING EQUATIONS.

- Boolean Equations can be directly derived from a truth table or from the logic Diagram.

- Likewise a truth table or logic diagram can be constructed from the Boolean equations.

- Each input variable group that produces a logical 1 in a truth table output column can form a term in a Boolean Switching equation.

- For Example, in the following truth table, the output variable  $M_1$  is a 1 in four cases.

| $S_3$ | $S_2$ | $S_1$ | $M_4$ | $M_3$ | $M_2$ | $M_1$ |

|-------|-------|-------|-------|-------|-------|-------|

| 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0     | 0     | 1     | 1     | 0     | 0     | 1     |

| 0     | 1     | 0     | 1     | 0     | 1     | 0     |

| 0     | 1     | 1     | 1     | 0     | 0     | 1     |

| 1     | 0     | 0     | 1     | 1     | 0     | 0     |

| 1     | 0     | 1     | 1     | 0     | 0     | 1     |

| 1     | 1     | 0     | 1     | 1     | 1     | 0     |

| 1     | 1     | 1     | 1     | 0     | 0     | 1     |

$\{S_3', S_2', S_1\}$ ,  $\{S_3', S_2, S_1\}$ ,  $\{S_3, S_2', S_1\}$  and  $\{S_3, S_2, S_1\}$ .

- The remaining input variable combinations cause output  $M_1$  to be a logical 0.

- A boolean equation can be written that defines all the conditions under which output  $M_1$  is a logical 1.

- Each term in the equation is formed by ANDing the input variables. Each AND term is then ORed with the other AND terms to complete the output Boolean equation.

- For  $M_1$ , the boolean equation would be written as

$$M_1 = S_3' S_2' S_1 + S_3' S_2 S_1 + S_3 S_2' S_1 + S_3 S_2 S_1$$

- Each AND term (Product term) identifies one input condition where the output is a 1.

1. LITERAL: A literal is a Boolean variable or its complement. For instance, let  $x$  be a binary variable, then both  $x$  and  $x'$  would be literals.

2. PRODUCT TERM: A Product term is a literal or the logical product (AND) of multiple literals.

For instance, let  $x, y$  and  $z$  be the binary variables. Then a representative product term could be  $x, xy, xyz$  or  $x'yz$  etc. . .

3. SUM TERM: A sum is a literal or the logical OR of multiple literals. Let  $x, y$  and  $z$  be the binary variables. Then a representative sum term could be  $x, x'+y$ , or  $x+y'+z'$  etc. . .

4. SUM OF PRODUCTS: A sum of Products (SOP) is the logical OR of multiple product terms. Each product term is the AND of binary literals.

For ex:  $xy' + x'y + x'yz + x'y'z'$  is a SOP Expression.

5. PRODUCT OF SUMS: A Product of <sup>SUMS (POS)</sup> is the logical AND of multiple OR terms. Each sum term is the OR of binary literals.

For ex:  $(x+y')$   $(x+y+z')$   $(y'+z')$  is a POS expression.

6. MINTERM: A minterm is a special case product (AND) term. A minterm is a product <sup>term</sup> that contains all of the input variables (each literal no more than once) that make up a boolean expression.

7. MAXTERM: A maxterm is a special case sum (OR) term. A maxterm is a sum term that contains all of the input variables (each literal no more than once) that make up a boolean expression.

8. CANONICAL SUM OF PRODUCTS: A canonical sum of products is a complete set of minterms that defines when an output variable is a logical 1.

Each minterm corresponds to the row in the truthtable where the output function is 1 i.e., the SOP for the output M in the following table is

$$M = a'b'ms + ab'ms + ab'ms.$$

| a | b | m | s | M |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

9. CANONICAL PRODUCT OF SUMS: A canonical product of sums is a complete set of maxterms that defines when an output is a logical 0.

Each maxterm corresponds to a row in the truthtable where the output is a 0

i.e., the pos for the output  $O_1$  in the following table is

$$O_1' = (C_1 + C_2 + C_3)' (C_1' + C_2 + C_3)' (C_1' + C_2' + C_3)' * (C_1' + C_2' + C_3')$$

| $C_1$ | $C_2$ | $C_3$ | $O_1$                               |

|-------|-------|-------|-------------------------------------|

| 0     | 0     | 0     | 0                                   |

| 0     | 0     | 1     | 1 $\leftarrow (C_1 + C_2 + C_3)'$   |

| 0     | 1     | 0     | 1 $\leftarrow (C_1 + C_2' + C_3)'$  |

| 0     | 1     | 1     | 1 $\leftarrow (C_1 + C_2' + C_3)'$  |

| 1     | 0     | 0     | 0 $\leftarrow (C_1' + C_2 + C_3)'$  |

| 1     | 0     | 1     | 0 $\leftarrow (C_1' + C_2 + C_3)'$  |

| 1     | 1     | 0     | 0 $\leftarrow (C_1' + C_2' + C_3)'$ |

| 1     | 1     | 1     | 0 $\leftarrow (C_1' + C_2' + C_3)'$ |

The table 1.1 shows the complete nature of minterms and maxterms.

- An input variable is complemented when it has value 0 if we are writing minterms.

- The input variables are complemented when they have a value 1, if we are writing maxterms.

- Minterms represent output variable 1s and maxterms represent output variables 0s.

- Lower case m is used to denote a minterm and Upper case M is used to denote a maxterm.

- The number subscript indicates the decimal value of the term.

| abc | MINTERM  |             | MAXTERM      |             |

|-----|----------|-------------|--------------|-------------|

|     | TERM     | DESIGNATION | TERM         | DESIGNATION |

| 000 | $a'b'c'$ | $m_0$       | $(a+b+c)$    | $M_0$       |

| 001 | $a'b'c$  | $m_1$       | $(a+b+c')$   | $M_1$       |

| 010 | $ab'c$   | $m_2$       | $(a+b'+c)$   | $M_2$       |

| 011 | $a'b'c$  | $m_3$       | $(a+b'+c')$  | $M_3$       |

| 100 | $ab'c'$  | $m_4$       | $(a'+b+c)$   | $M_4$       |

| 101 | $a'b'c$  | $m_5$       | $(a'+b+c')$  | $M_5$       |

| 110 | $abc'$   | $m_6$       | $(a'+b'+c)$  | $M_6$       |

| 111 | $abc$    | $m_7$       | $(a'+b'+c')$ | $M_7$       |

Table 1.1 - Minterm &amp; Maxterm Designations

- output equations can be directly from the truth table using either minterms or maxterms.

- when an output equation is written in minterms or maxterms, it is a canonical expression.

## CANONICAL FORMS

- Canonical is a word used to describe a condition of a switching equation.

- In normal use the word means "conforming to a general rule". The rule for switching logic, is that each term used in a switching equation must contain all of the available input variables.

- Two formats generally exist for expressing switching equations in a Canonical form.

- ① Sum of Minterms (Products)

- ② Product of Maxterms. (sums)

- Canonical expressions are not simplified why canonical forms???.

- ① Situations that occurs when logic designer must manipulate Boolean equations for purposes other than simplification.

- ② Conversion from one form to another form (TTL Nand Gates to ECL NOR Gates)

- ③ Entry into the Karnaugh map.

## 1. SOP Equation to Canonical form.

11.11

To place a SOP equation to canonical form using Boolean algebra, we do the following.

(i) Identify the missing variable(s) in each AND term.  $(xy)$

(ii) AND the missing term and its complement with the original AND term.

$$xy(z+z')$$

Because  $(z+z') = 1$ , the original AND term value is not changed.

(iii) Expand the term by application of the property of distribution

$$xy(z+z') = xyz + xyz'$$

## 2. POS Equation to canonical form

To place a POS equation to canonical form using Boolean Algebra, we do this

(i) Identify the missing variables in each OR term.  $(x+y')$

(ii) OR the missing terms and its complement with the original OR term.

Original :  $x+y'$

Modified :  $(x+y'+\underline{zz'})$   $\swarrow$  using missing variable

→ Because  $zz' = 0$ , the original <sup>+ its complement</sup> term value is not changed.

(iii) Expand the term by application of distributive property.

$$(x+y'+zz') = (x+y'+z) (x+y'+z')$$

### GENERATION OF SWITCHING EQUATIONS FROM

#### TRUTH TABLES

- Switching equations can be written more conveniently by using the minterm or maxterm numerical designation as shown in Table 1.1 (pg. No 1.10), instead of writing the variable names or their complements.

- m and M designation can be dropped and the decimal equivalent value for

the term can be written directly.

### 1. CANONICAL SOP EQUATION

For ex: consider the canonical SOP equation

$$P = ab'c + ab'c' + abc' + abc + a'b'e$$

- For decode each of the minterms based on binary weighting of each variable and produce a list of decimal decoded minterms , the result would be

$$P = \Sigma(5, 4, 6, 7, 3)$$

- To keep the input variable notation from being lost in a minterm list the relationship  $P = f(a, b, c)$  is used.

- This means that the output variable  $P$  is a function of the set of input variables  $\{a, b, c\}$  with input variable  $a$  being the most significant bit (MSB).

- The sign  $\Sigma$  indicates summation and stands for the sum of products canonical form.

- When numbers in a decimal decoded set are preceded by a  $\Sigma$  sign , a

SOP expression is indicated. Each number represents a minterm.

$$P = f(a, b, c) = (ab'c + ab'c' + abc' + abc + a'b'c)$$

$$= \sum (5, 4, 6, 7, 3)$$

## 2. CANONICAL POS EQUATION

- Canonical POS expressions can be written in similar fashion as SOP expressions.

- $\Pi (P_i)$  sign is used to indicate POS canonical form.

- The decimal number listed in a POS set represents maxterms.

- The input variable names are indicated in the same manner as in SOP equations.

$$X = f(A, B, C)$$

- Maxterms are complement of minterms.

## KARNAUGH MAPS.

- Simplification of switching equations reduces the amount of hardware needed to realize a given function.

- Reduction of gates and gate inputs may result in fewer integrated circuits, which in turn decreases cost and improves reliability.

- Boolean Algebra can be used to simplify equations but the process is lengthy and error prone.

- It is required a systematic method for finding and eliminating any redundancies in an equation.

- A better approach is the use of Karnaugh map. The Karnaugh map is a matrix of squares. Each square represents minterm or maxterm from a boolean expression / equation. The arrangement of the matrix square permits identification of input variables redundancies, which helps reduce the output equation.

- The Karnaugh map identifies all of the cases for a given set of input variables where groups of minterms may contain redundant variables of the form  $x+x'=1$ . When these groups are identified, the redundant variables can be eliminated resulting in a simplified output function.

- If a given switching equation contains a minterm, then a 1 is entered into the square that represents that term. A maxterm is represented by a 0.

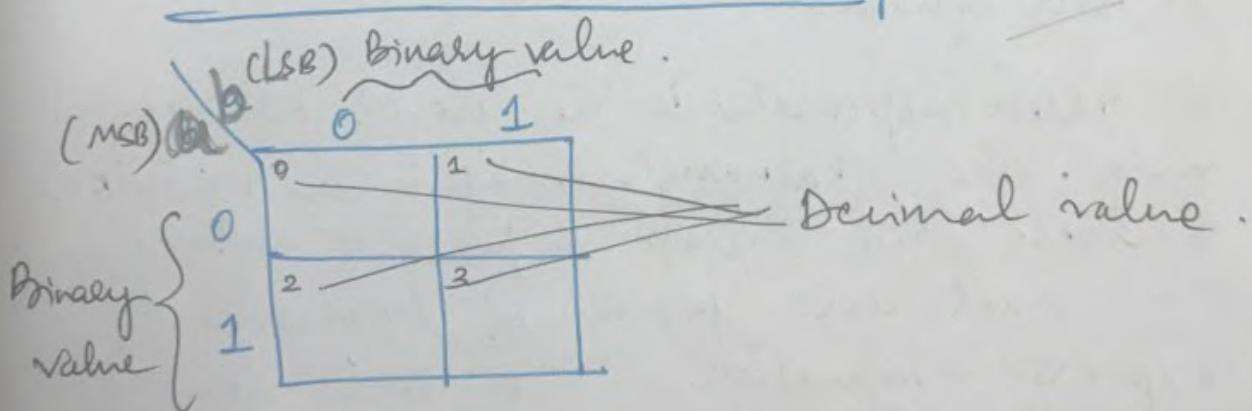

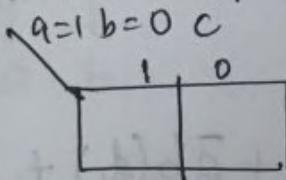

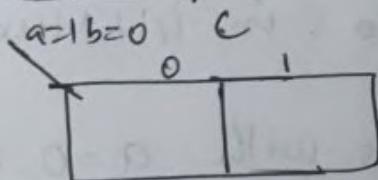

### Two Variable K-Map

- All four possible combinations of input variables are represented.

## THREE AND FOUR VARIABLE KARNAUGH MAPS.

- The fig represents three-variable Karnaugh map.

AB (MSB)

LSB C

|   |   | 00 | 01 | 11 | 10 |               |

|---|---|----|----|----|----|---------------|

|   |   | 0  | 2  | 6  | 4  | Decimal value |

| 0 | 1 | 3  | 7  | 5  |    |               |

| 1 |   |    |    |    |    |               |

- Each square in the map represents a possible minterm or maxterm of a 3-variable function.

- The upper-left square represents binary 000, minterm ( $A'B'C'$ ) or maxterm ( $A+B+C$ ).

- As three binary variables can represent eight (8) unique combinations, we find 8 squares are needed.

- If minterm  $A'B'C'$  (000) occurred in a switching equation, then a 1 would be inserted into the upper-left square.

- Assignment of a square to each of the 8 minterms resulting from 3-input variables results in given Table -

| Inputs | Minterm | Maxterm |

|--------|---------|---------|

| A B C  | m       | M       |

| 0 0 0  | 0       | 0       |

| 0 0 1  | 1       | 1       |

| 0 1 0  | 2       | 2       |

| 0 1 1  | 3       | 3       |

| 1 0 0  | 4       | 4       |

| 1 0 1  | 5       | 5       |

| 1 1 0  | 6       | 6       |

| 1 1 1  | 7       | 7       |

- We may label the decimal value for each square in a Karnaugh map by decoding the binary numbers as shown in fig( ).

- Across the top and down side of the 3 variable K-map only one bit changes occur between adjacent squares for each column and row

- Each adjacent row or column differs by only one variable.

## 1.15

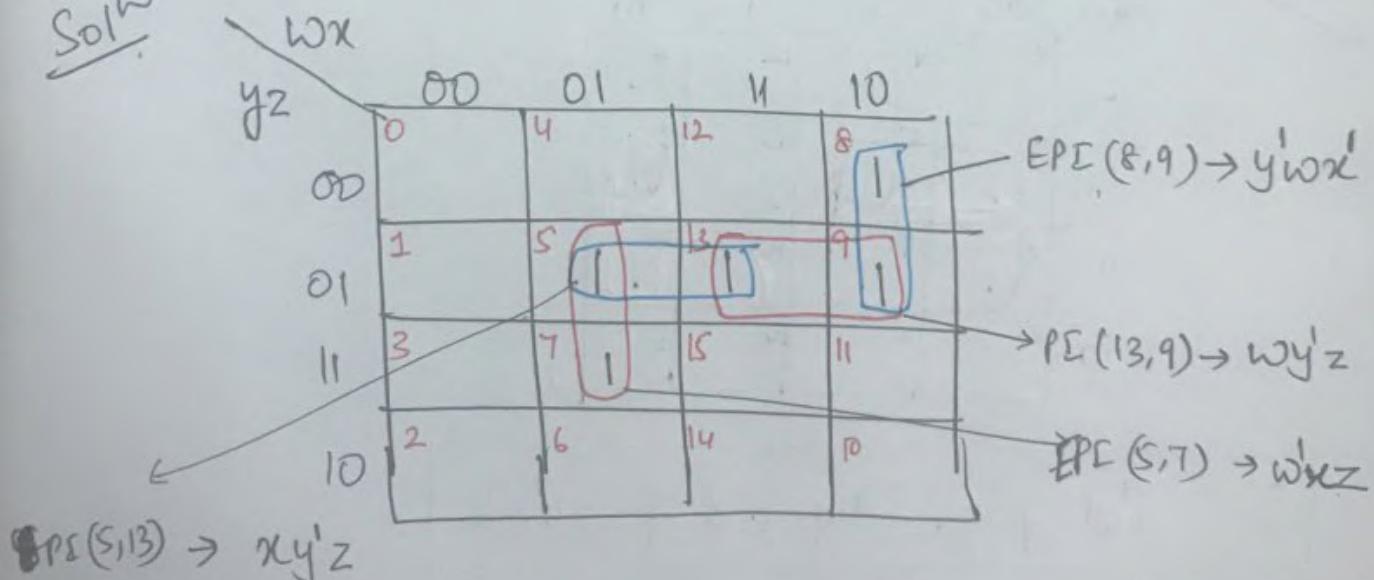

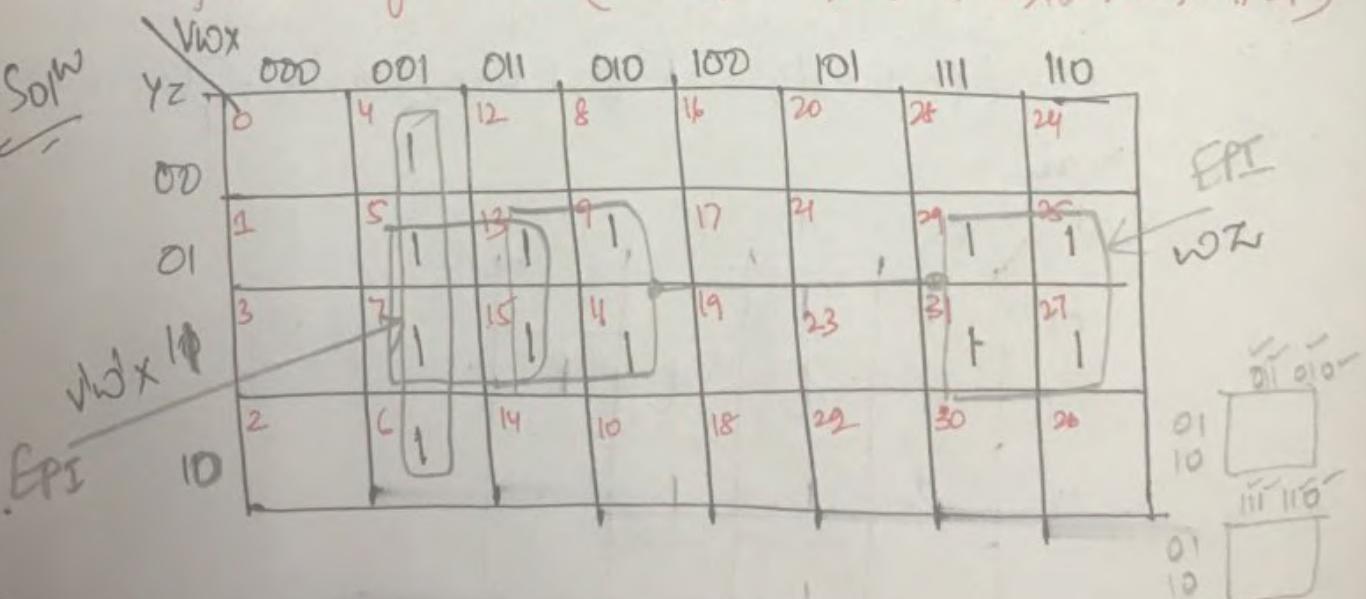

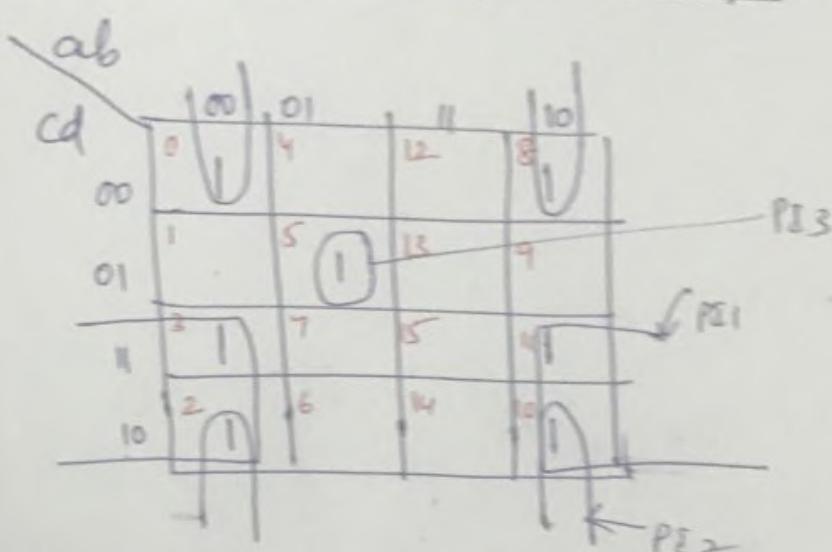

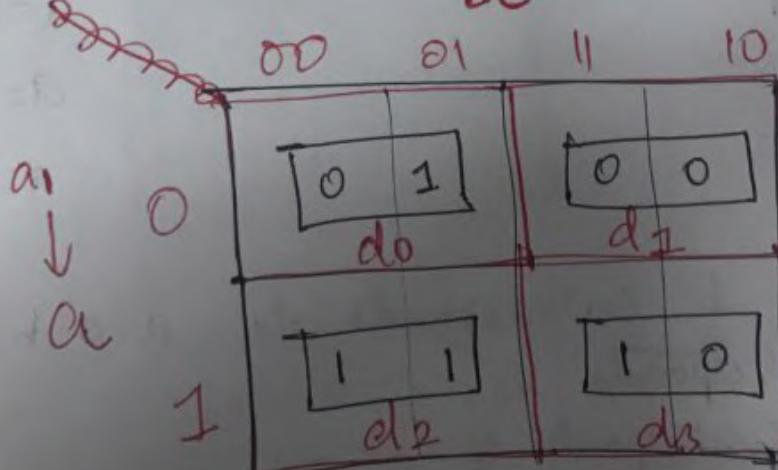

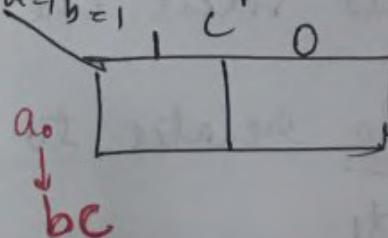

## FOUR VARIABLE K-MAP

- is the same length both horizontally and vertically.

- Variable representation is the same in both directions, two variables across (00, 01, 10, 11) and two down.

- The Input variable binary weighting is  $W = 2^3 = 8$ ,  $X = 2^2 = 4$ ,  $Y = 2^1 = 2$ ,  $Z = 2^0 = 1$

$\text{W} \rightarrow \text{MSB}$ ,  $\text{Z} \rightarrow \text{LSB}$  .

$\text{W} \times \text{X} \rightarrow \text{MSB}$ ,  $\text{Y} \times \text{Z} \rightarrow \text{LSB}$  .

Binary values for  $\text{W} \times \text{X}$ .

Decimal values

$P_5 \rightarrow ?$ .

$EPI \rightarrow ?$ .

|                                              |    | 00 | 01 | 11 | 10 |

|----------------------------------------------|----|----|----|----|----|

|                                              |    | 0  | 4  | 12 | 8  |

| Binary values for $\text{Y} \times \text{Z}$ | 00 | 1  | 5  | 13 | 9  |

|                                              | 01 | 3  | 7  | 15 | 11 |

|                                              | 10 | 2  | 6  | 14 | 10 |

|                                              | 11 |    |    |    |    |

fig(): Four variable K-Map.

- Loading K-map involves writing 1 in the squares corresponding to a minterm or a 0 in the square corresponding to a maxterm.

STEPS INVOLVED IN LOADING & DETERMINING

THE ESSENTIAL PRIME IMPlicants.

Step 1: Load the minterms into the 2-map by placing a 1 in the appropriate square.

Step 2: Look for groups of minterms (PI)

(a) Group size must be a power of 2

( $\because$  of Binary number system)

(b) PIs are formed from groups of minterms whose size is a power of 2. Minterm group size that are not an integer power of 2 are not permitted.

- Find the largest groups of minterms first, then progressively evaluate smaller collections of minterms until all groups are found.

Step 3: Once all of the possible PIs have been identified, we determine whether any have minterms that are unique? If so, that PI is an Essential Prime Implicant (EPI)

Step 4 : Select all essential prime implicants and a minimal set of remaining prime implicants that cover all remaining 1s in the K-Map.

Step 5 : More than one equally simplified result is possible when more than one set of remaining PIs contain the same no. of minterms and maxterms.

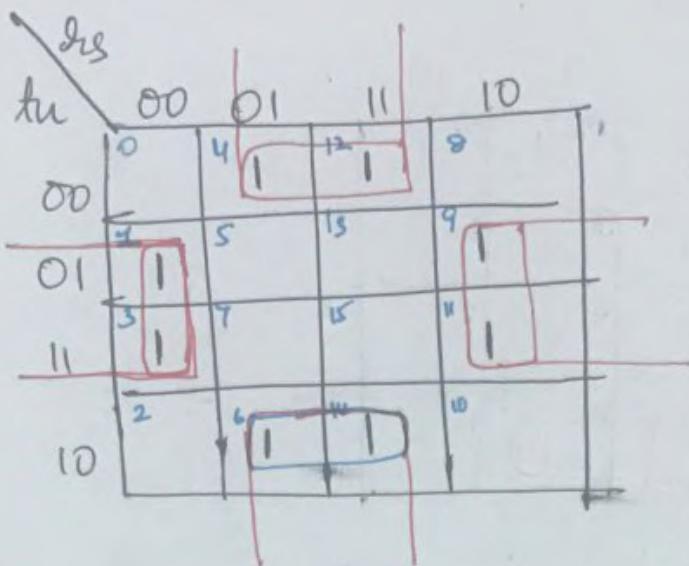

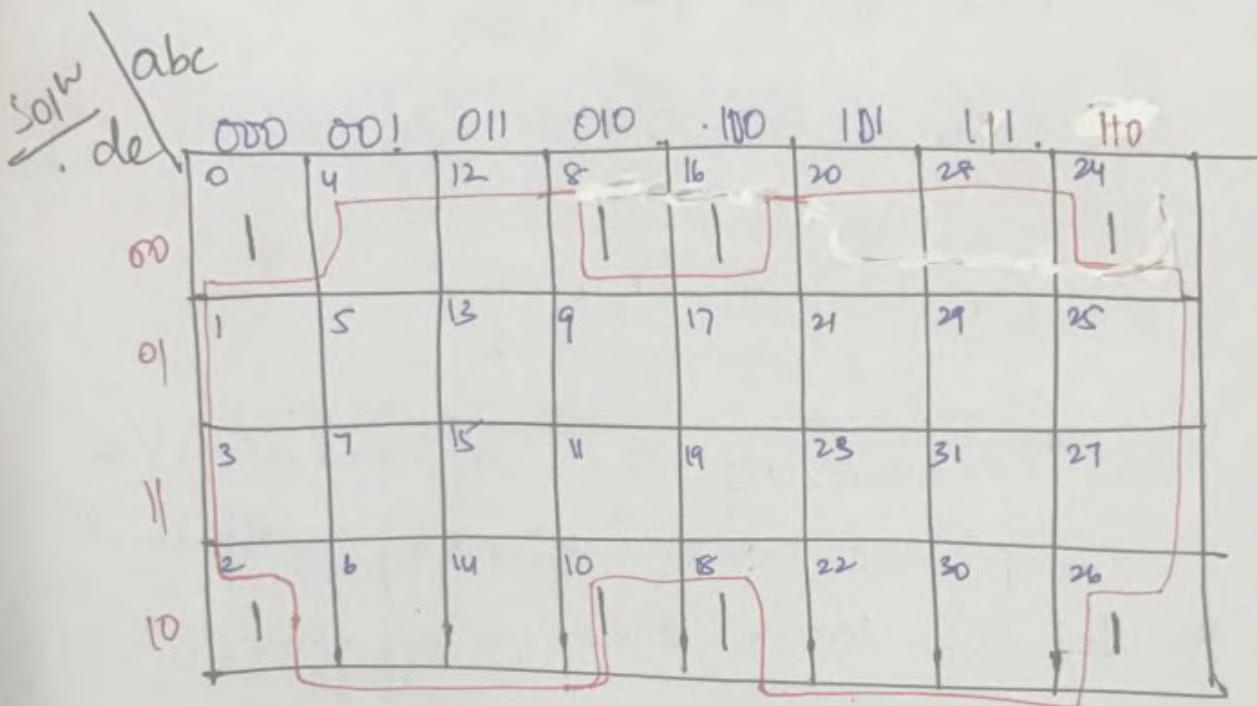

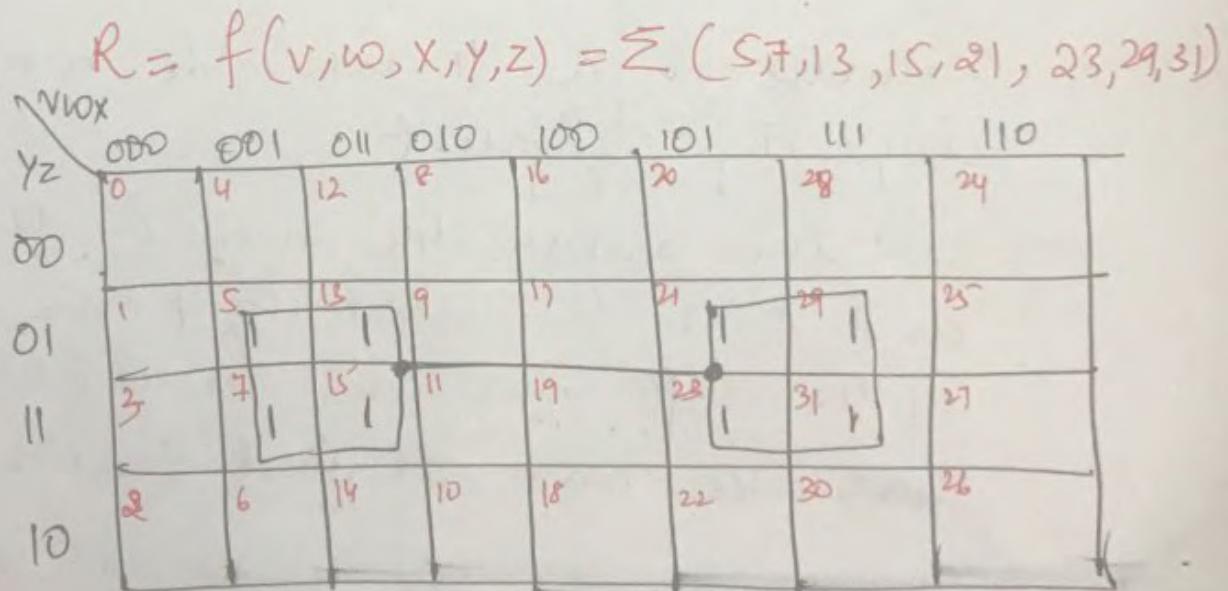

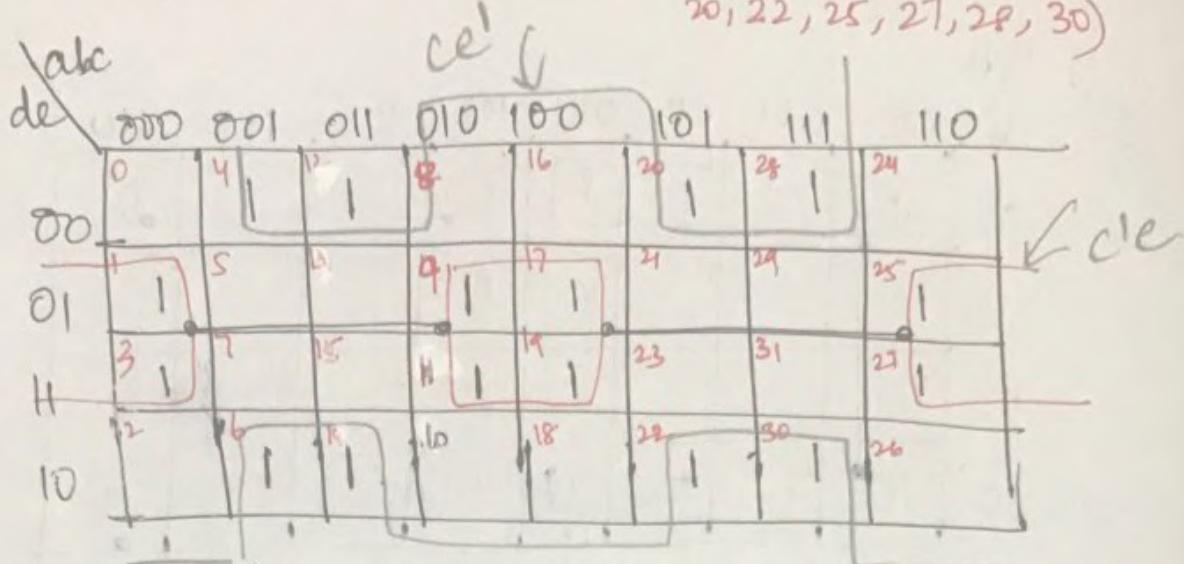

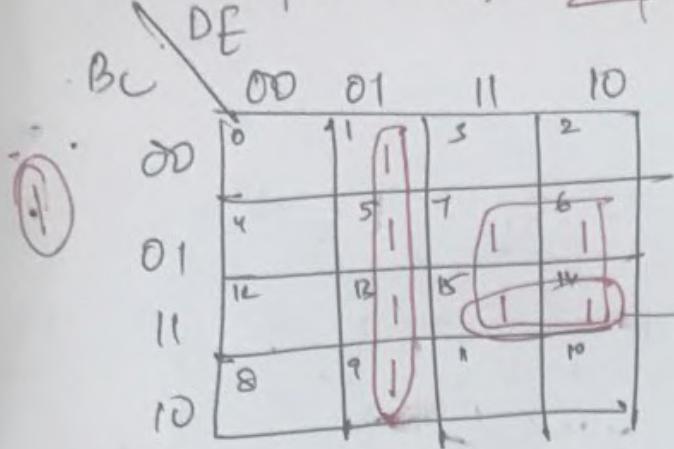

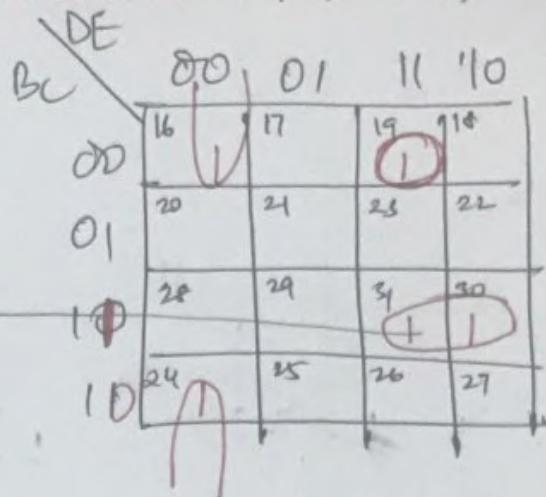

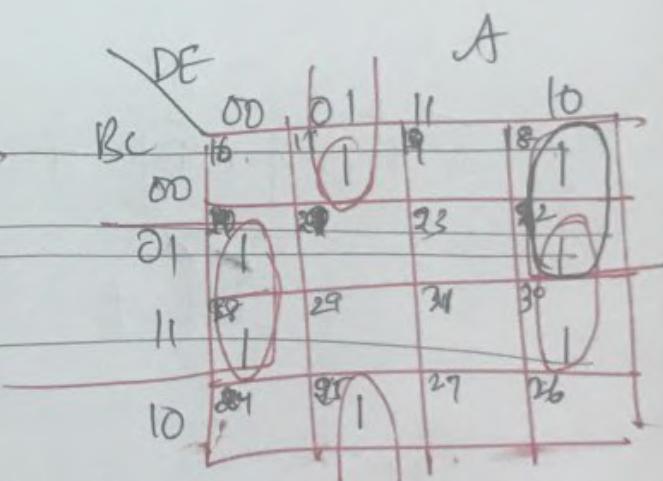

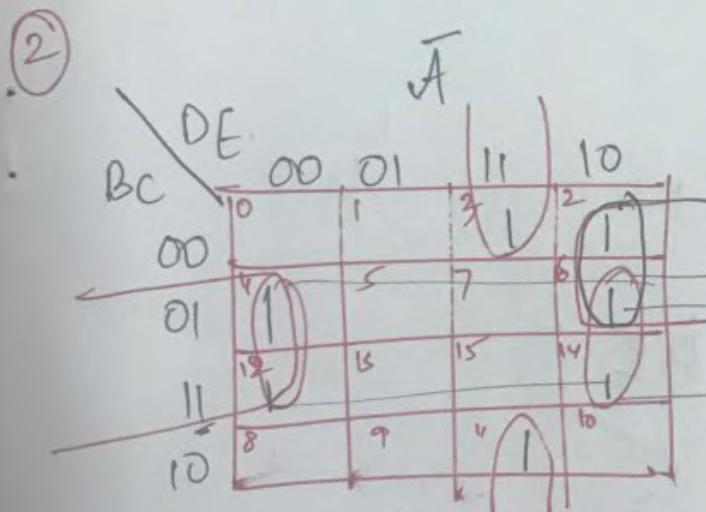

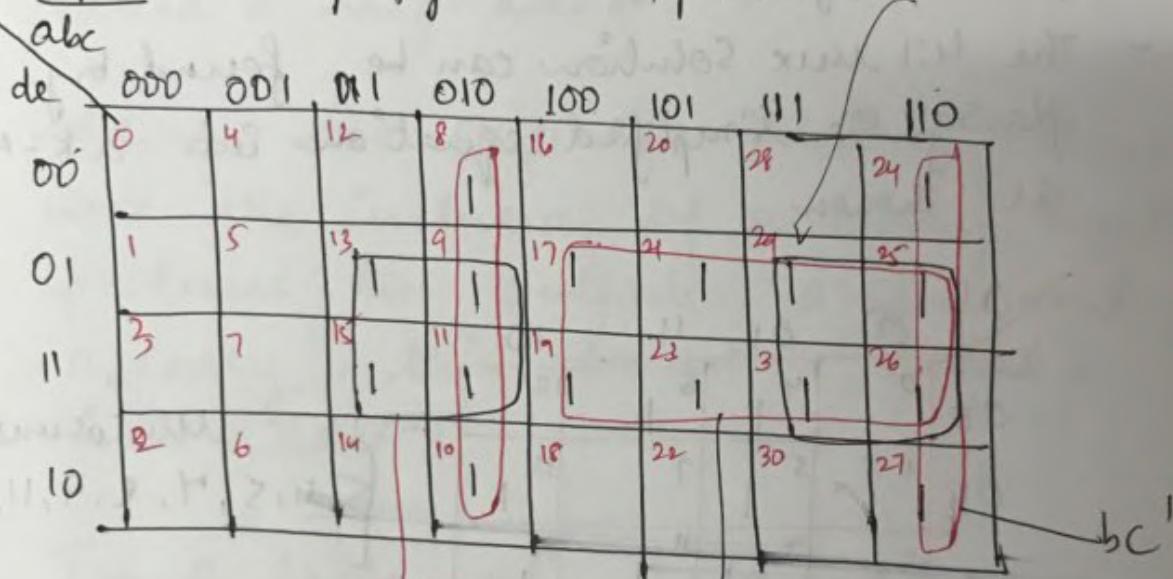

### FIVE VARIABLE K-MAP.

- Five Variable K-maps can be constructed so that 3-variables are laid out horizontally and 2 vertically as shown.

ABC

| DE | 000 | 001 | 011 | 010 | 110 | 111 | 101 | 100 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|

| 00 | 0   | 4   | 12  | 8   | 24  | 28  | 20  | 16  |

| 01 | 1   | 5   | 13  | 9   | 25  | 29  | 21  | 7   |

| 11 | 3   | 7   | 15  | 11  | 27  | 31  | 23  | 19  |

| 10 | 2   | 6   | 14  | 10  | 26  | 30  | 22  | 18  |

fig( ) : 5-variable K-Map.

- A, B, C, D, E are the input variables.

- $2^5$  possible combinations exist, ranging from  $(00000)_2$  to  $(11111)_2$ .

$$\begin{aligned}

A &\leftarrow \text{MSB} \quad 2^4 = 16 \\

B &\quad \quad \quad 2^3 = 08 \\

C &\quad \quad \quad 2^2 = 04 \\

D &\quad \quad \quad 2^1 = 02 \\

E &\leftarrow \text{LSB} \quad 2^0 = 01

\end{aligned}$$

- The decimal value associated with each square in the map is found by adding the column and row values.

- Each half of the five-variable map corresponds to a single 4-variable K-Map.

STACKED VERSION OF 5-Variable K-MAP.

| ABC |   | DE  |     |     |     |     |     |     |     |

|-----|---|-----|-----|-----|-----|-----|-----|-----|-----|

|     |   | 000 | 001 | 011 | 010 | 110 | 111 | 101 | 100 |

| 00  | 0 | 4   | 12  | 8   | 24  | 28  | 20  | 16  |     |

| 01  | 1 | 5   | 13  | 9   | 25  | 29  | 21  | 17  |     |

| 11  | 3 | 7   | 15  | 11  | 27  | 31  | 23  | 19  |     |

| 10  | 2 | 6   | 14  | 10  | 26  | 30  | 22  | 18  |     |

$\rightarrow$  4-Variable K-Map  $\rightarrow$  4-Variable K-Map.

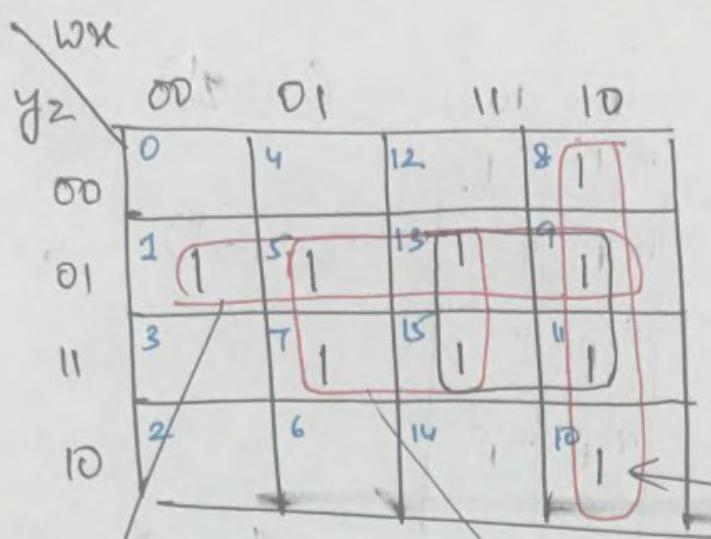

## INCOMPLETELY SPECIFIED FUNCTIONS.

### (DON'T CARE TERMS)

- when an output value is known for every possible combination of input variables, the function is said to be completely specified.

- when an op value is not known for every combination of input variables, usually because all combinations cannot occur, the function is said to be incompletely specified.

- The minterms or maxterms that are not used as a part of the output function are called don't care terms.

- For ex: Binary to Ex-3 BCD as shown in Table.

- BCD codes including Ex-3 can represent only a single digit decimal character (0 to 9)

- The decimal number 9 takes 4-bits in Ex-3 BCD code.

- Input combinations (10, 11, 12, 13, 14, 15) in decimal are not used to specify any output variable

Value : outputs A, B, C, D are incompletely specified for those Enpt code values that are don't care terms.

Truth table for Binary to Ex-3 BCD code conversion.

| Binary<br>wxyz | Ex-3 BCD<br>ABCD |

|----------------|------------------|

| 0000           | 0011             |

| 0001           | 0100             |

| 0010           | 0101             |

| 0011           | 0110             |

| 0100           | 0111             |

| 0101           | 1000             |

| 0110           | 1001             |

| 0111           | 1010             |

| 1000           | 1011             |

| 1001           | 1100             |

| 1010           | Don't care       |

| 1011           | — " —            |

| 1100           | — " —            |

| 1101           | — " —            |

| 1110           | — " —            |

| 1111           | — " —            |

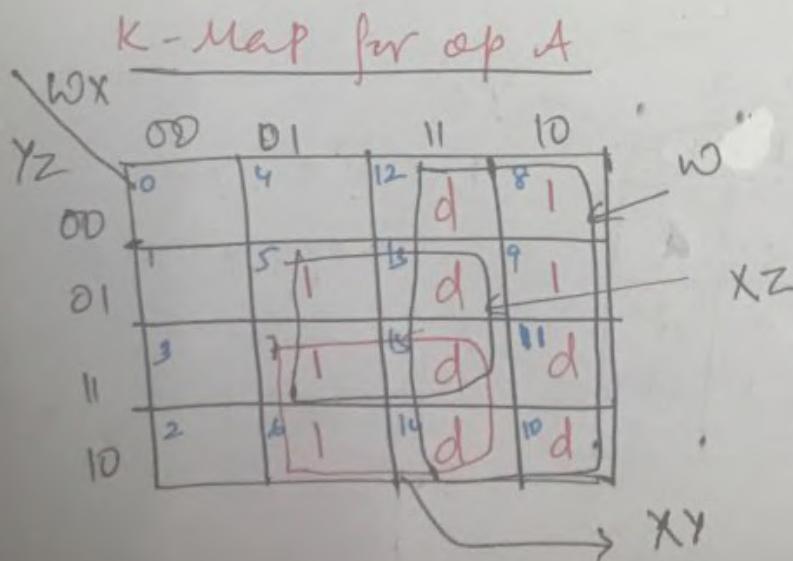

- Writing the equations for output variables A, B, CD, including the don't care terms, we get.

$$A = f(w, x, y, z) = \sum (5, 6, 7, 8, 9) + \sum d(10, 11, 12, 13, 14, 15)$$

$$B = f(w, x, y, z) = \sum (1, 2, 3, 4, 9) + \sum d(10, 11, 12, 13, 14, 15)$$

$$C = f(w, x, y, z) = \sum (0, 3, 4, 7, 8) + \sum d(10, 11, 12, 13, 14, 15)$$

$$D = f(w, x, y, z) = \sum (0, 2, 4, 6, 8) + \sum d(10, 11, 12, 13, 14, 15)$$

- Don't care terms are distinguished from regular minterms in that it does not matter whether we assign them a value of 0 or 1, because these input combinations never occur.

- Don't care terms are indicated by a d in each of the k-maps.

$$\therefore A = w + xz + xy$$

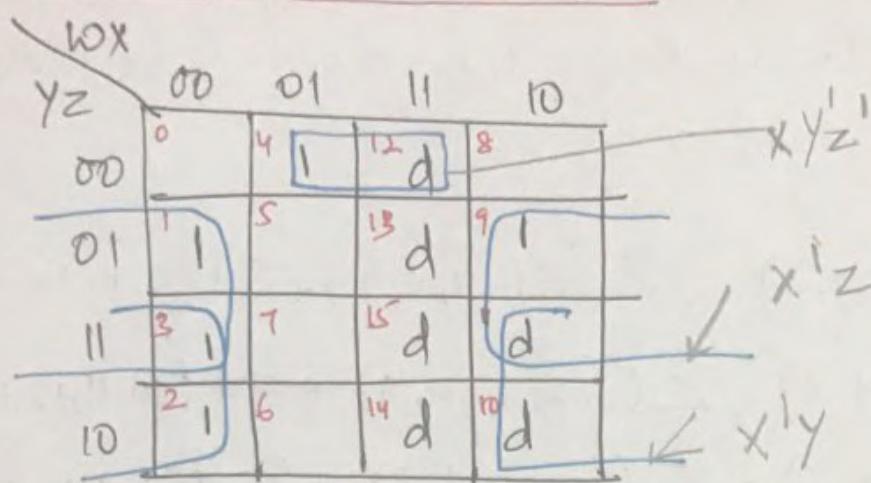

### K-Map for op B.

$$B = x'y'z' + x'z + x'y$$

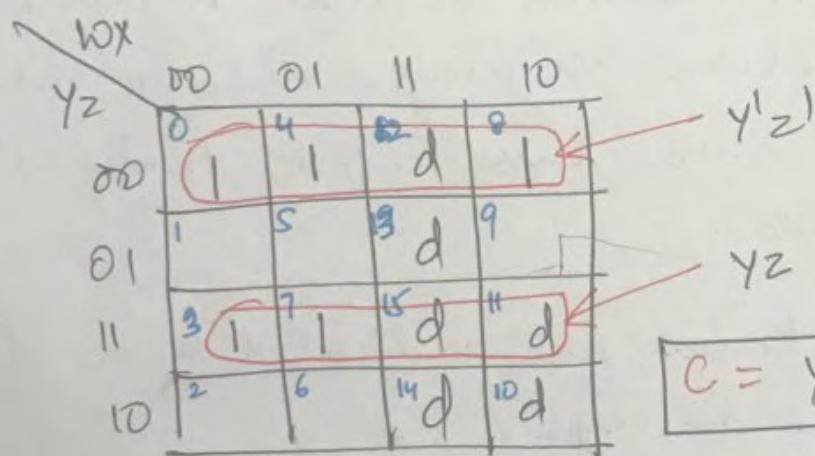

### K-Map for op C.

$$C = yz + y'z' = y \oplus z$$

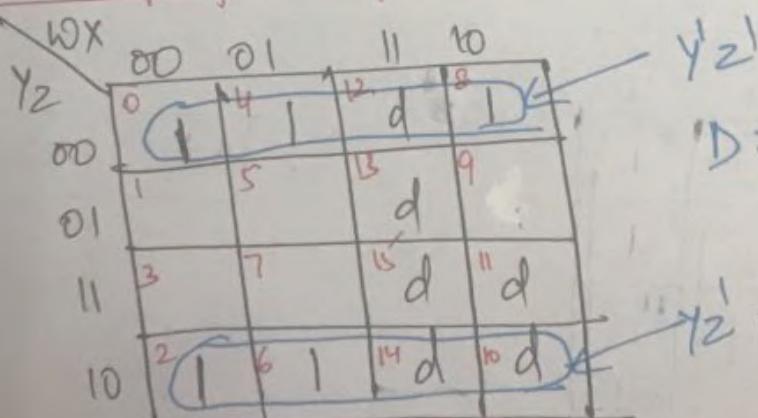

### K-Map for op D.

$$\begin{aligned} D &= y'z' + yz' \\ &= (y + y')z' = z' \end{aligned}$$

$$D = z'$$

## Procedure for the determination and use of don't care terms.

- ① → Develop the truth table that describes the input/output relationship.

- ② → Determine if all of the input combinations are used to generate the ops.

- (a) If so, then no don't care terms exist.

- (b) If not, then those combinations of input variables not used to determine output values are don't care terms.

- ③ → Once the don't care terms have been identified, use a separate symbol in the K-Map squares.

- ④ → Create as large as EPI grouping as possible, including don't care terms that have been combined with normal minterms.

- ⑤ → Do not group don't care terms by themselves. A don't care PI is meaningless, because don't care terms are not used to generate the output function.

The other are found.

The school have all the equipment

Consist of a number of desks

and chairs and desks with

the old window.

## QUINE - MC CLUSKEY MINIMIZATION TECHNIQUE.

- For many applications, the no. of variables in a problem is too large to simplify manually using K-maps.

- Simplification typically means that a logic designer can obtain more functional use from a given component. Therefore some automatic or computer driven simplification routine is desirable.

- The QUINE - MC CLUSKEY minimization technique is an algorithm that uses the same boolean Algebra postulates that were used with Karnaugh Maps but in a form suitable for a computer solution.

- Large K-maps require recognition of group of terms that may form essential prime implicants. The larger the map, the more difficult this pattern recognition becomes.

- The QM approach eliminates the need for such pattern recognition.

Ex: Simplify the following using the QM minimization technique.

$$D = f(a, b, c, d) = \Sigma(0, 1, 2, 3, 6, 7, 8, 9, 14, 15).$$

Case 1

Soln Using K-Map.

$$D = b'c' + bc + a'b'$$

or

$$D = b'c' + bc + a'c.$$

Case 2 : QM Technique.

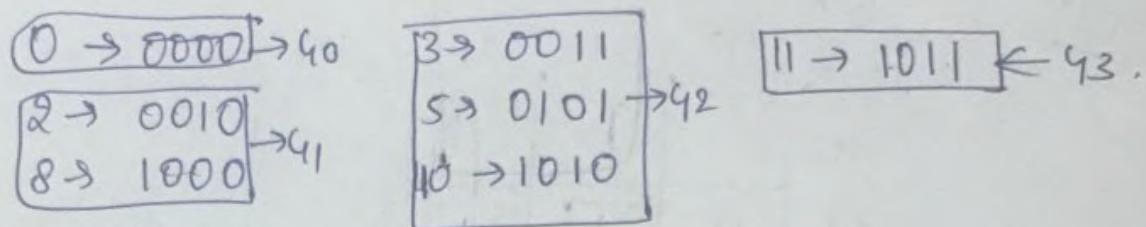

Step 1: Arrange all of the minterms, in a list of increasing order, so that groups of terms contain the same no. of 1s.

- Each minterm in the original expression is arranged in increasing order according to no. of 1's contained each group.

- Group 0 contains no. 0s., group 1 contains only those minterms that have single 1 (1,2,8), group 2 contains minterms with two 1s (3,6,9), group 3 contains minterms with three 1s (7,14) and group 4 contains minterms with four 1's (15).

|         |                       |                       |                      |                      |         |

|---------|-----------------------|-----------------------|----------------------|----------------------|---------|

| Group 0 | $0 \rightarrow 0000$  | $1 \rightarrow 0001$  | $2 \rightarrow 0010$ | $8 \rightarrow 1000$ | Group 1 |

|         | $3 \rightarrow 0011$  | $6 \rightarrow 0110$  | $9 \rightarrow 1001$ |                      | Group 2 |

|         | $7 \rightarrow 0111$  | $14 \rightarrow 1110$ |                      |                      | Group 3 |

|         | $15 \rightarrow 1111$ |                       |                      |                      | Group 4 |

Grouping minterms according to no. of 1s.

| Group | Minterm | ab cd |

|-------|---------|-------|

| 0     | 0       | 0000  |

| 1     | 1       | 0001  |

| 1     | 2       | 0010  |

| 1     | 8       | 1000  |

| 2     | 3       | 0011  |

|       | 6       | 0110  |

|       | 9       | 1001  |

| 3     | 7       | 0111  |

|       | 14      | 1110  |

| 4     | 15      | 1111  |

Table 1.

Step 2 : Create a new table showing the minterms in group n (ex: 0) that matched with those from group  $n+1$  (1) such that they differ in only one position.

- compare minterm  $\{0\}$  in group 0 of Table 1 with each of minterms in group 1. When all the minterms in group 0 have been compared with those in group 1.

- Compare the <sup>minterms in</sup> group 1 with those in group 2.

- This process is repeated until all of the minterms in each group have been compared to those of in the next higher group.

- When a minterm in a group combined with a minterm in adjacent group, a dash (-) is used to indicate an eliminated variable.

- The combined minterms are grouped together in Table 2. - Each combination results in a new minterm group.

Table 2: Creation of minteum groups of two.

1.22

| Group | Minteum | a | b | c | d |   |

|-------|---------|---|---|---|---|---|

| 0     | 0,1     | 0 | 0 | 0 | - | ✓ |

|       | 0,2     | 0 | 0 | - | 0 | ✓ |

|       | 0,8     | - | 0 | 0 | 0 | ✓ |

| 1     | 1,3     | 0 | 0 | - | 1 | ✓ |

|       | 1,9     | - | 0 | 0 | 1 | ✓ |

|       | 2,3     | 0 | 0 | 1 | - | ✓ |

|       | 2,6     | 0 | - | 1 | 0 | ✓ |

|       | 8,9     | 1 | 0 | 0 | - | ✓ |

| 2     | 3,7     | 0 | - | 1 | 1 | ✓ |

|       | 6,7     | 0 | 1 | 1 | - | ✓ |

|       | 6,14    | - | 1 | 1 | 0 | ✓ |

| 3     | 7,15    | - | 1 | 1 | 1 | ✓ |

|       | 14,15   | 1 | 1 | 1 | - | ✓ |

- As each minteum, combines with a minteum in the next higher group is checked (✓), indicating that it is now part of a larger group.

Step 3 : All of the adjacent minterm groups contained in Table ② are compared to see if groups of 4 can be made.

- The criteria for forming groups of 4 are as follows :

- (a) The dashes in the groups of two must be in the same bit position and

- (b) only one variable change is allowed.

- A comparison is made of each minterm in group  $n$  with each minterm in group  $n+1$ . Those that meet the criteria are combined in a larger group as shown in Table ③.

| group | Minterm      | a b c d |

|-------|--------------|---------|

| 0     | 0, 1, 2, 3   | 0 0 --  |

| 0     | 0, 1, 8, 9   | - 0 0 - |

| 1     | 2, 6, 3, 7   | 0 - 1 - |

| 2     | 6, 7, 14, 15 | - 1 1 - |

Table 3: Creation of minterms of group of 4.

Step 4: Minterms  $\{0, 1\}$  in group 0 is compared with  $\{2, 3\}$  in group 1, to form a group  $\{0, 1, 2, 3\}$

- If the dashes (-) are in the same position and only one variable changes then a newer group is created.

- This process is repeated until no further combination is possible. That is each minterm in group  $n$  is compared with each minterm in group  $n+1$  in Table ②.

Step 5 → All nonchecked minterm groups are now considered as PIs.

Step 6 → All of the PIs are formed into a PI Table as shown in Table ④.

| PI terms        | Decimal      | 0 | 1 | 2 | 3 | 6 | 7 | 8 | 9 | 14 | 15 |

|-----------------|--------------|---|---|---|---|---|---|---|---|----|----|

| $a'b'$          | 0, 1, 2, 3   | x | x | x | x |   |   |   |   |    |    |

| $b'c'$          | 0, 1, 8, 9   | x | x |   |   |   |   | x | x |    |    |

| $a'c$           | 2, 6, 3, 7   |   |   | x | x | x | x |   |   |    |    |

| $\checkmark bc$ | 6, 7, 14, 15 |   |   | x | x |   |   | x | x | x  | x  |

Table 4: Prime Implicant Table.

- The prime implicant table lists each of the minterms contained in the original switching equation across the top of the table.

- Each PI is listed vertically in 2 forms. PI terms and the decimal list of minterms that make up the PI.

Step 7 → Evaluate the prime implicants by circling those minterms that are contained in only one PI (only one x in a column).

- The minterms (8, 9, 14, 15) meet this condition → Essential PI.

- (0, 1, 8, 9) & {6, 7, 14, 15} are EPI.

- Minterms {2, 3} are contained in 2 PIs {0, 1, 2, 3} & {2, 3, 6, 7}. we need one or the other of these PIs to cover minterms in the equation but not both.

$$\boxed{

\begin{aligned}

D &= b'c' + bc + a'b' \\

\text{or} \\

D &= b'c' + bc + a'c

\end{aligned}

}$$

## QUINE-MC CLUSKY USING DON'T CARE TERMS

1.24

- The same rules that applied to using don't care terms with the K-map are appropriate for QM technique.

Ex:  $S = f(w, x, y, z) = \sum (1, 3, 13, 15) + \sum d(8, 9, 10, 11)$

Step 1: Construct a list of minterms and don't care terms classified according to the number of 1s. Indicate the don't care terms by using a \* symbol. Don't care terms are never included as prime implicants by themselves.

|                        |                        |                         |                       |

|------------------------|------------------------|-------------------------|-----------------------|

| $1 \rightarrow 0001$   | $3 \rightarrow 0011$   | $13 \rightarrow 1101$   | $15 \rightarrow 1111$ |

| $8^* \rightarrow 1000$ | $9^* \rightarrow 1001$ | $10^* \rightarrow 1100$ | Group 4               |

| Group | minterm              | w x y z                       |

|-------|----------------------|-------------------------------|

| 1     | 1<br>$8^*$           | 0 0 0 1<br>1 0 0 0            |

| 2     | 3<br>$9^*$<br>$10^*$ | 0 0 1 1<br>1 0 0 1<br>1 1 0 0 |

| 3     | $11^*$<br>13         | 1 0 1 1<br>1 1 0 1            |

| 4     | 15                   | 1 1 1 1                       |

Table 1: Grouping of Minterms.

Step 2 : compare terms in group  $n$ ,

including don't care terms in group

$n+1$ , for a single variable change.

- Treat don't care terms as a 1 in

finding PIs.

| group | Minterm   | wxyz  |

|-------|-----------|-------|

| 1     | (1, 3)    | 00-1✓ |

| 1     | (1, 9*)   | -001✓ |

| 1     | (8, 9*)   | 100-✓ |

| 1     | (8, 10*)  | 10-0✓ |

| 2     | (3, 11*)  | 1011- |

| 2     | (9*, 11*) | 10-1✓ |

| 2     | (9*, 13)  | 1-01✓ |

| 2     | (0*, 11*) | 101-  |

| 3     | (11*, 15) | 1+11✓ |

| 3     | (13, 15)  | 11-1✓ |

Table 2: Minterm groups of two.

Step 3 : Repeat Step 2 to create a table of group of 4 minterms and don't care terms. Repeat Step 3 until no further grouping can occur.

| Group | Minterms         | wxyz    |

|-------|------------------|---------|

| 1     | 1, 3, 9*, 11*    | - 0 - 1 |

| 1     | 8*, 9*, 10*, 11* | 1 0 --  |

| 2     | 9*, 13, 11*, 15  | 1 1 - 1 |

Table 3: Minterms groups of 4.

- Table 3 represents group of 4 Minterms and don't care terms. Each term is EPI. But  $(8^*, 9^*, 10^*, 11^*)$  contains only don't care terms  $\therefore$  not a PI.

Step 4 : Creation of PI Table

| PI terms | Decimal      | Minterms |   |    |    |

|----------|--------------|----------|---|----|----|

|          |              | 1        | 3 | 13 | 15 |

| $x'z$    | 1 3 9* 11*   | ⊗        | ⊗ |    |    |

| $wz$     | 9* 11* 13 15 |          |   | ⊗  | ⊗  |

$$\therefore S = wz + x'z$$

Problems:

1. Place the following equation into proper canonical form.

a)  $P = f(a, b, c) = ab' + ac' + bc$  (SOP)

Sol<sup>n</sup>:  $P = ab'(c+c') + ac'(b+b') + bc(a+a')$

$= ab'c + \underline{ab'c'} + abc' + \underline{abc'} + abc + a'bc$

$\therefore P = ab'c + ab'c' + abc' + abc + a'bc.$

b)  $Q = f(w, x, y, z) = w'x + yz'$  (SOP)

$$\begin{aligned}

Q &= w'x(y+y')(z+z') + yz'(x+x')(w+w') \\

&= xyw'z + xyw'z' + xw'w'z' + \underline{xyw'z'} \\

&\quad + \underline{xywz'} + xyw'z' + x'yw'z' + \underline{x'yw'z'} \\

&= xyw'z + xyw'z' + xy'w'z' + xyw'z' + xywz' \\

&\quad + \underline{x'ywz'} + x'yw'z'

\end{aligned}$$

$$(c) \quad T = f(a, b, c) = (a+b') (b'+c) \quad (\text{Pos.})$$

Sol<sup>w</sup>

$$\begin{aligned} T &= (a+b') (b'+c) \\ &= (a+b'+cc') (aa'+b'+c) \\ &= \cancel{(a+b'+c)} (a+b'+c') \cancel{(a'+b'+c)} \\ &= (a+b'+c) (a+b'+c') (a'+b'+c) \end{aligned}$$

$$(d) \quad J = f(A, B, C, D) = (A+B'+C) (A'+D) \quad \text{Pos.}$$

$$\begin{aligned} J &= (A+B'+C) (A'+D) \\ &= (A+B'+C+DD') (A'+B+B'+CC'+D) \\ &= (A+B'+C+D) (A+B'+C+D') \\ &\quad (A'+B+C+D) (A'+B+C'+D) \quad \cancel{(A'+B'+C+D)} \\ &\quad \cancel{(A'+B'+C+D)} (A'+B'+C'+D) \end{aligned}$$

2. Write the canonical minterm and maxterm expressions for the following table

④

|   | ip |   |   |   | op |                          |

|---|----|---|---|---|----|--------------------------|

|   | a  | b | m | s | M  | Minterm Expression       |

| 0 | 0  | 0 | 0 | 0 | 0  |                          |

| 0 | 0  | 0 | 0 | 1 | 0  | $M = f(a, b, m, s)$      |

| 0 | 0  | 1 | 0 | 0 |    |                          |

| 0 | 0  | 1 | 1 | 0 |    | $= \sum(7, 11, 15)$      |

| 0 | 1  | 0 | 0 | 0 |    |                          |

| 0 | 1  | 0 | 1 | 0 |    | $= a'b'ms + ab'ms + abm$ |

| 0 | 1  | 1 | 0 | 0 |    |                          |

| 0 | 1  | 1 | 1 | 1 |    | <u>Maxterm Expr</u>      |

| 1 | 0  | 0 | 0 | 0 |    |                          |

| 1 | 0  | 0 | 1 | 0 |    | $M = f(a, b, m, s)$      |

| 1 | 0  | 1 | 0 | 0 |    |                          |

| 1 | 0  | 1 | 1 | 0 |    |                          |

|   |    |   |   |   |    |                          |

| 1 | 1  | 0 | 0 | 0 |    |                          |

| 1 | 1  | 0 | 1 | 0 |    |                          |

| 1 | 1  | 1 | 0 | 0 |    |                          |

| 1 | 1  | 1 | 1 | 1 |    |                          |

(b)

|   | Inputs |       |       | Outputs |       |       |            |

|---|--------|-------|-------|---------|-------|-------|------------|

|   | $c_1$  | $c_2$ | $c_3$ | $o_1$   | $o_2$ | $o_3$ | $w_1, w_2$ |

| 0 | 0      | 0     | 0     | 0       | 1     | 1     | 0, 0       |

| 1 | 0      | 0     | 1     | 1       | 1     | 0     | 0, 0       |

| 2 | 0      | 1     | 0     | 1       | 0     | 1     | 0, 0       |

| 3 | 0      | 1     | 1     | 1       | 0     | 0     | 1, 0       |

| 4 | 1      | 0     | 0     | 0       | 1     | 1     | 0, 0       |

| 5 | 1      | 0     | 1     | 0       | 1     | 0     | 1, 0       |

| 6 | 1      | 1     | 0     | 0       | 0     | 1     | 1, 0       |

| 7 | 1      | 1     | 1     | 0       | 0     | 0     | 0, 1       |

Minterm Expressions

$$o_1 = f(c_1, c_2, c_3) = c_1' c_2' c_3 + c_1' c_2 c_3' + c_1' c_2 c_3$$

$$= \sum (1, 2, 3)$$

$$o_2 = f(c_1, c_2, c_3) = c_1' c_2 c_3' + c_1' c_2' c_3 + c_1 c_2' c_3' + c_1 c_2 c_3$$

$$= \sum (0, 1, 4, 5)$$

$$o_3 = f(c_1, c_2, c_3) = c_1' c_2' c_3 + c_1' c_2 c_3 + c_1 c_2' c_3 + c_1 c_2 c_3$$

$$= \sum (0, 2, 4, 6)$$

$$w_1 = f(c_1, c_2, c_3) = c_1' c_2 c_3 + c_1 c_2' c_3 + c_1 c_2 c_3'$$

$$= \sum (3, 5, 6)$$

$$w_2 = f(c_1, c_2, c_3) = c_1' c_2 c_3'$$

$$= \sum 7$$

## Maxterm Expressions

$$O_1 = f(c_1, c_2, c_3) = \pi(0, 4, 5, 6, 7)$$

$$O_2 = f(c_1, c_2, c_3) = \pi(2, 3, 6, 7)$$

$$O_3 = f(c_1, c_2, c_3) = \pi(1, 3, 5, 7)$$

$$w_1 = f(c_1, c_2, c_3) = \pi(0, 1, 2, 4, 7)$$

$$w_2 = f(c_1, c_2, c_3) = \pi(0, 1, 2, 3, 4, 5, 6)$$

3. Express the following SOP equations in a minterm list.

a.  $H = f(A, B, C) = \sum_{011}^{A'B'C} + \sum_{001}^{AB'C} + \sum_{111}^{ABC}$

$= \sum(3, 1, 7)$

b.  $g_2 = f(w, x, y, z) = \sum_{1110}^{wxyz'} + \sum_{1010}^{wx'y'z'} + \sum_{0110}^{w'xyz'} + \sum_{0010}^{w'x'y'z'}$

$= \sum(2, 6, 10, 14)$

4. Express the following POS equation in a maxterm list.

a.  $T = f(a, b, c) = (a + b' + c) (a + b' + c') (a' + b' + c)$

$= \pi(2, 3, 6)$

$$\text{.b. } J = f(A, B, C, D) = (A + B' + C + D) (A' + B + C + D) \\ (A + B' + C + D') (A' + B' + C + D) \\ (A' + B + C' + D) (A' + B' + C' + D)$$

$$(A, B, C, D) = \pi(4, 5, 8, 10, 12, 14)$$

5. Write the POS & SOP equations for  $A$  &  $A'$  for the following Truth table.

|   | X | Y | Z | A | $A'$ |

|---|---|---|---|---|------|

| 0 | 0 | 0 | 0 | 0 | 1    |

| 1 | 0 | 0 | 1 | 0 | 1    |

| 2 | 0 | 1 | 0 | 1 | 0    |

| 3 | 0 | 1 | 1 | 0 | 1    |

| 4 | 1 | 0 | 0 | 1 | 0    |

| 5 | 1 | 0 | 1 | 0 | 1    |

| 6 | 1 | 1 | 0 | 0 | 1    |

| 7 | 1 | 1 | 1 | 0 | 1    |

SOP for  $A$

$$A = \Sigma(2, 4, 5)$$

SOP for  $A'$

$$A' = \Sigma(0, 1, 3, 6, 7)$$

POS for  $A$

$$A = \pi(0, 1, 3, 6, 7)$$

SOP for  $A' \rightarrow A' = \pi(2, 4, 5)$

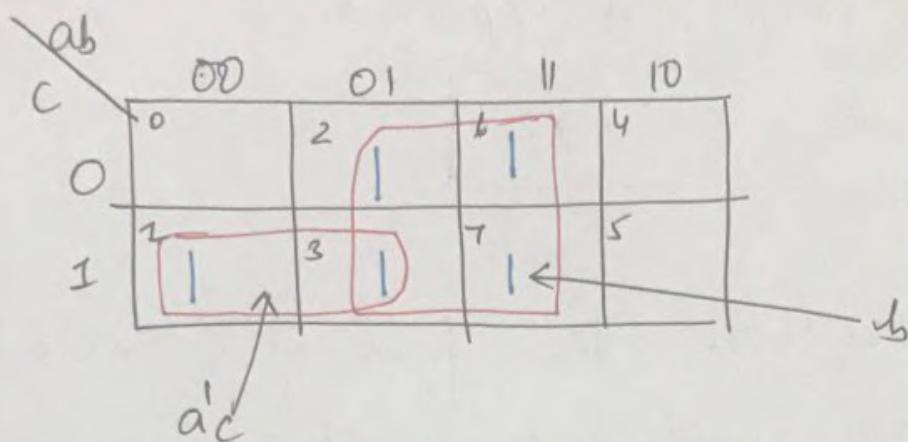

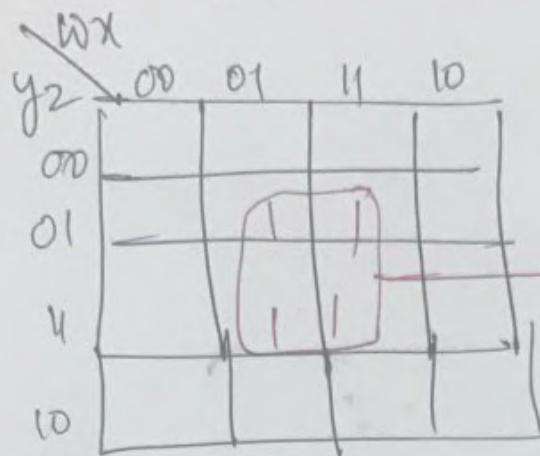

## Problems on K-Map.

① Simplify the Boolean function using K-map.

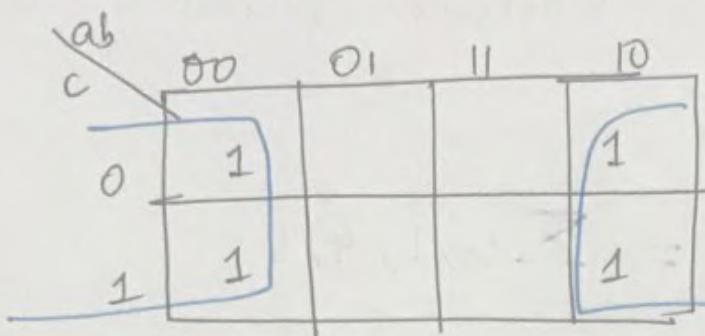

$$Y = f(a, b, c) = \sum 0, 1, 4, 5$$

Soln

|   | ab | 00 | 01 | 11 | 10 |

|---|----|----|----|----|----|

| c | 0  | 1  | 0  | 0  | 1  |

| a | 0  | 1  | 0  | 0  | 1  |

| b | 0  | 1  | 0  | 0  | 1  |

$$\begin{aligned}

Y &= a'b'c' + a'b'c + a'b'c' \\

&\quad + a'b'c \\

&= a'b'(c+c') + a'b'(c+c') \\

&= a'b' + a'b

\end{aligned}$$

- Two groups of minterms

$$Y = a'b' + ab'$$

or

|   | ab | 00 | 01 | 11 | 10 |

|---|----|----|----|----|----|

| c | 0  | 1  | 0  | 0  | 1  |

| a | 0  | 1  | 0  | 0  | 1  |

| b | 0  | 1  | 0  | 0  | 1  |

one group of

4 minterms.

$$Y = b'$$

$$Y = a'b'c' + a'b'c + a'b'c' + a'b'c$$

$$= a'b'(c+c') + a'b'(c+c')$$

$$= a'b' + a'b' = b'(a+a') = b'$$

3-variable K-map showing

Prime Implicant PI  $[0, 1, 4, 5]$ .

$2^n$  K-map

$n=3, m=2$

$(0, 1, 4, 5)$  forms a

prime implicant

# literals  $[n-m = 3-2 = 1]$

Remaining

$$Y = b'$$

X-X

- A set of  $2^n$  K-map squares are combined to form a Prime Implicant, if  $n$ -variables of the equation being simplified have a  $2^n$  permutations within the set and the remaining  $m-n$  variables have the same value within the set. The resulting product term has  $m-n$  literals.

- In other words  $2^n$  K-map squares may be combined to form a group of minterms containing  $m-n$  literals, where  $m$  represents the no. of variables in the original equation.

X - Any single minterm or permitted group of minterms is called an Implicant of an output function.

X - A prime implicant is a group of minterms that cannot be combined with any other minterms or groups.

- Minterms (0,1,4,5) are each implicants of  $y$ . The prime implicants consist of the 4 minterms grouped together.

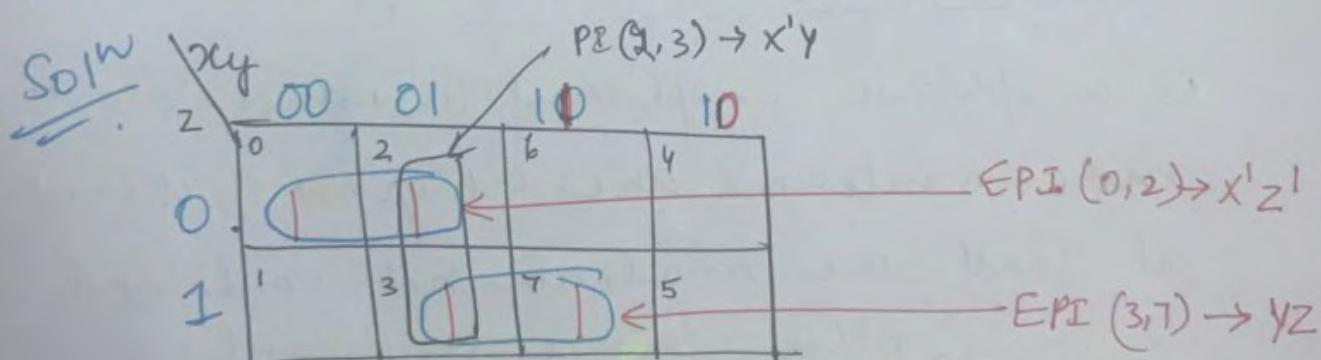

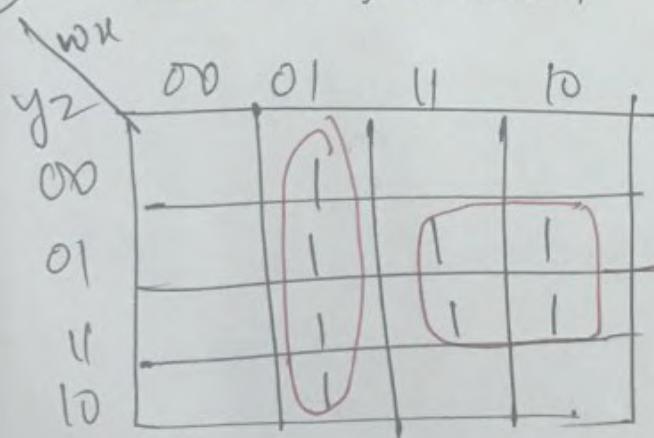

Q =  $f(x,y,z) = \sum(0,2,3,7)$

- Expression  $Q$  is loaded into the K-Map.

- 3 groups of minterms are found  $(0,2)$ ,  $(2,3)$  &  $(3,7)$

- Each of the 3 groups form a prime implicant.

Prime Implicant (0,2) reduces to  $x'z'$

by (2,3) reduced to  $x'y$

& (3,7) reduces to  $yz$ .

- Groups (0,2) and (3,7) both contain a minterm that is not in any other group.

Minterm (0) is unique to PI (0,2)

Minterm (7) is unique to PI (3,7).

An Essential Prime Implicant [EPI] is a prime implicant in which one or more minterms are unique i.e., it contains at least one minterm not contained in any other prime implicant.

- The simplified expression for Q includes only the essential prime implicants. The non essential prime implicant (2,3) term is redundant because all of its minterms are covered by the

two essential prime implicants.

The simplified expression is

$$Q = x'z' + yz$$

- Procedure for finding essential prime implicants is this

- find the prime implicants by finding all permitted maximum sized groups of minterms.

- find essential prime implicants by identifying those prime implicants that contain at least one minterm not found in any other prime implicant.

③

$$D = f(x, y, z) = \sum 0, 2, 4, 6$$

| xy\z | 00 | 01 | 11 | 10 |

|------|----|----|----|----|

| 0    | 0  | 2  | 6  | 4  |

| 1    | 1  | 1  | 1  | 1  |

| y\z  | 1  | 3  | 7  | 5  |

$$EPI(0, 2, 4, 6) \rightarrow z'$$

$$D = z'$$

④

$$Q = f(a, b, c) = \sum 1, 2, 3, 6, 7$$

Sol<sup>n</sup>

$$Q = b + a'c$$

- 2 Prime Implicants exist  $(1, 3)$  &  $(2, 3, 6, 7)$ . Both are essential because each has a unique minterm.

⑤

$$J = f(x, y, z) = \sum 0, 2, 3, 4, 5, 7$$

Sol<sup>n</sup>

- 6 minterms containing 2 minterms exist.

$$(0, 2) \rightarrow x'z'$$

$$(0, 4) \rightarrow y'z'$$

$$(2, 3) \rightarrow x'y$$

$$(3, 7) \rightarrow yz$$

$$(7, 5) \rightarrow xz$$

$$(4, 5) \rightarrow xy'$$

- The final simplified equation is not unique i.e., more than one equally simplified result is possible.

- The product terms in the simplified result must cover all of the minterms.

- For ex, we must pick a prime implicant  $(0, 2)$  or  $(0, 4)$  to cover the minterm  $(0)$ .

- Two equally simplified equations are

$$J = x'z' + xy' + yz$$

or

which covers  $(0, 2, 3, 4, 5, 7)$

$$J = y'z' + x'y + xz$$

which covers  $(0, 2, 3, 7, 4, 5)$

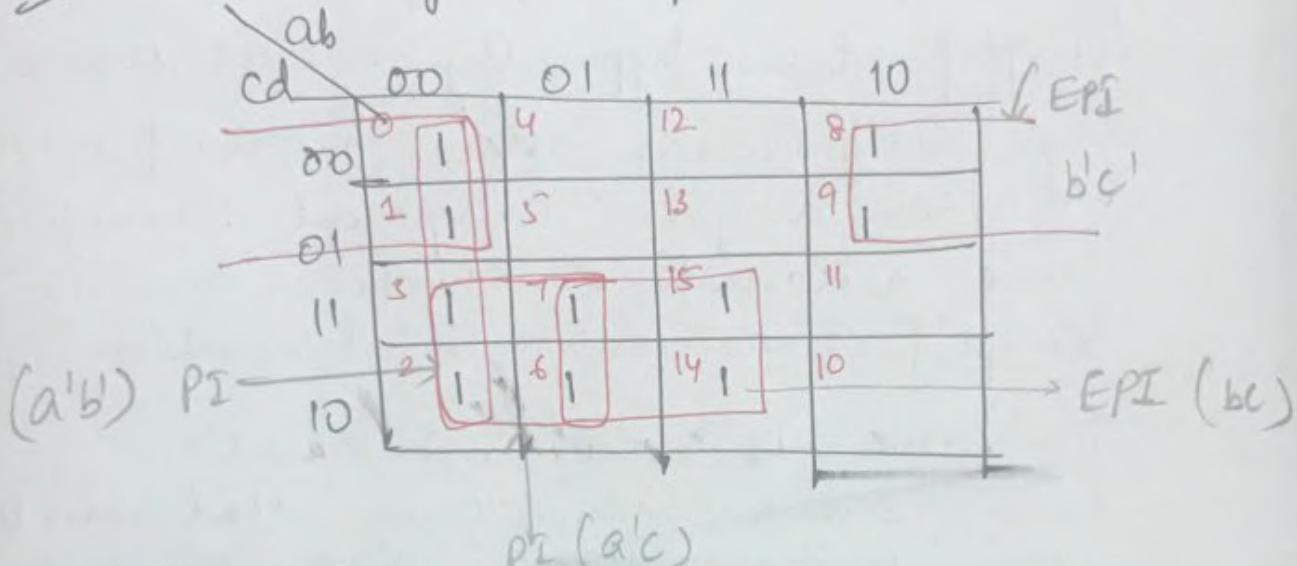

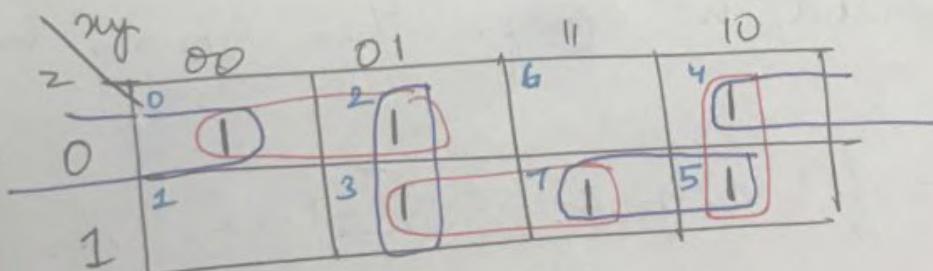

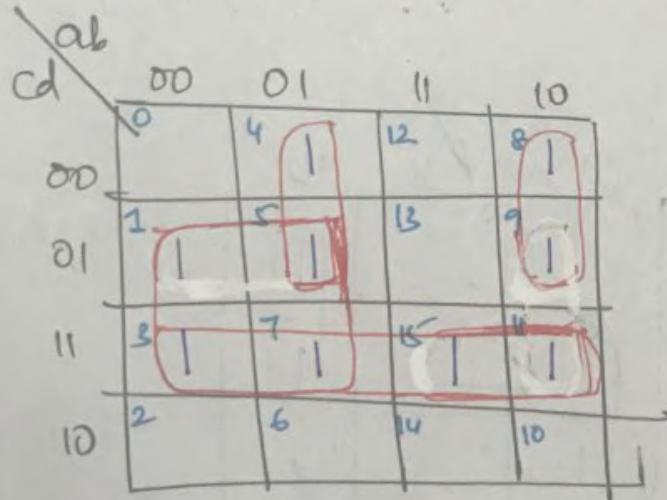

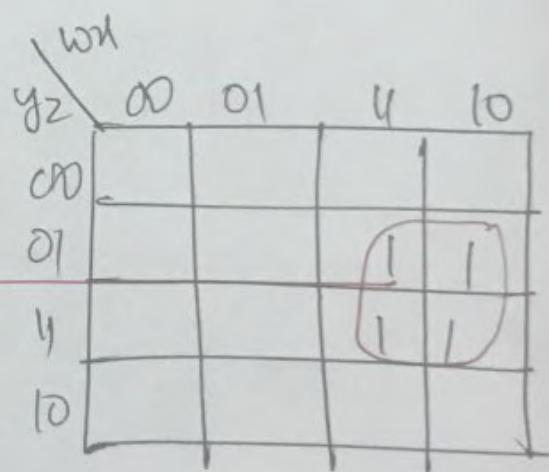

⑥ Simplify the following 4-variable equations.

$$k = f(w, x, y, z) = \sum 0, 1, 4, 5, 9, 11, 13, 15$$

- 3 four variable Prime Implicants are present  $\{0, 1, 4, 5\}$   $\{9, 11, 13, 15\}$  &  $\{1, 5, 9, 13\}$

- 2 EPI are present  $\{0, 1, 4, 5\}$   $\{9, 11, 13, 15\}$

- Prime Implicant  $\{1, 5, 9, 13\}$  is not essential because all of its minterms are contained in other 2 prime implicants.

- The final simplified eqn is

$$K = w'y' + wz$$

①  $L = f(a, b, c, d) = \sum 0, 2, 5, 7, 8, 10, 13, 15$

Soln

$$\begin{aligned}

L &= bd + b'd' \\

L &= (b \oplus d)' \\

&= b \odot d

\end{aligned}$$

(8)

(P8)

$$P = f(r, s, t, u) = \sum (1, 3, 4, 6, 9, 11, 12, 14)$$

Solv

$$P = s u' + s' u = s \oplus u$$

(9)

$$D = f(w, x, y, z) = \sum (5, 7, 8, 9, 13)$$

Solv

$$D = w'xz + wx'y' + xy'z$$

$$D = w'xz + wx'y' + wy'z$$

(10)

$$P = f(a, b, c, d) = \sum(0, 1, 2, 4, 5, 6, 8, 9, 12, 13, 14)$$

SOLW

$$P = c' + a'd' + \underline{bd'}$$

(11)

$$S = f(a, b, c, d) = \sum(1, 3, 4, 5, 7, 8, 9, 11, 15)$$

SOLW

$$S = a'd + \underline{a'bc'} + cd + ab'c'$$

(12)

(P9)

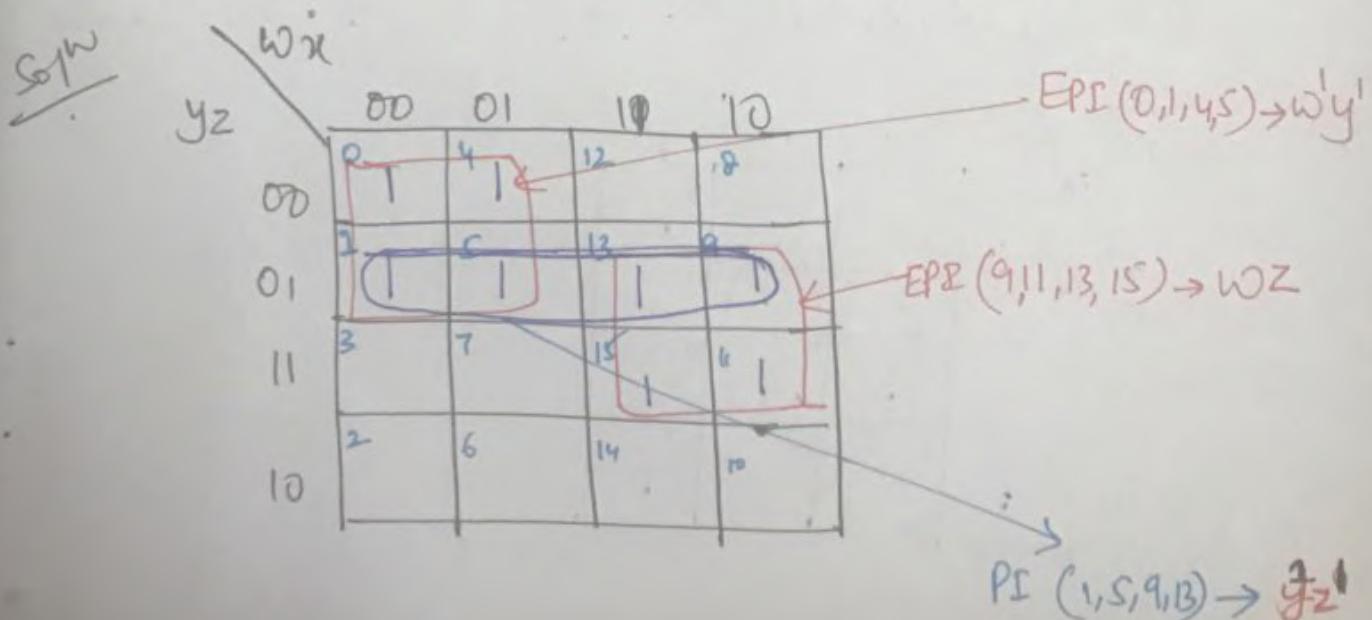

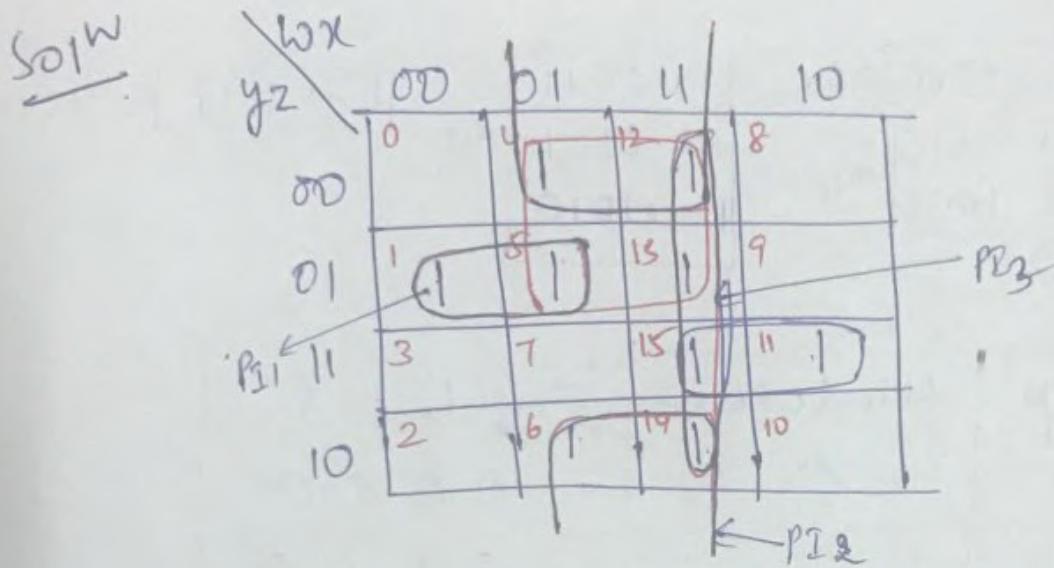

$$f(w, x, y, z) = \sum (1, 5, 7, 8, 9, 10, 11, 13, 15)$$

SOLW.

$$EPI (8, 9, 10, 11) \rightarrow w x'$$

$$EPI (1, 5, 9, 13) \rightarrow y z$$

$$EPI (5, 7, 13, 15) \rightarrow x z$$

$$U = y' z + w x' + x z$$

(13)

Simplify.

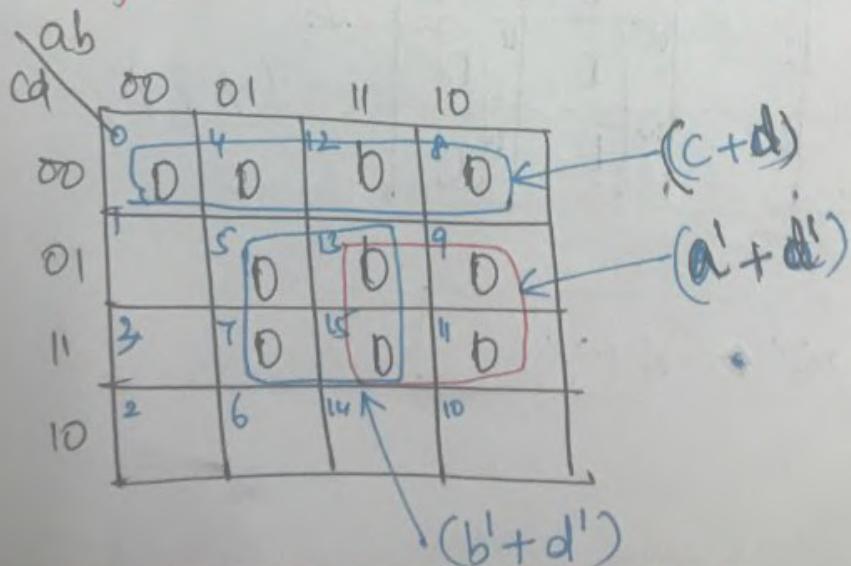

$$G = f(a, b, c, d) = \pi(0, 4, 5, 7, 8, 9, 11, 12, 13, 15)$$

SOLW.

$$(c + d)$$

$$(a' + d')$$

$$(b' + d')$$

$$G = (c + d)(b' + d')(a' + d')$$

(14)

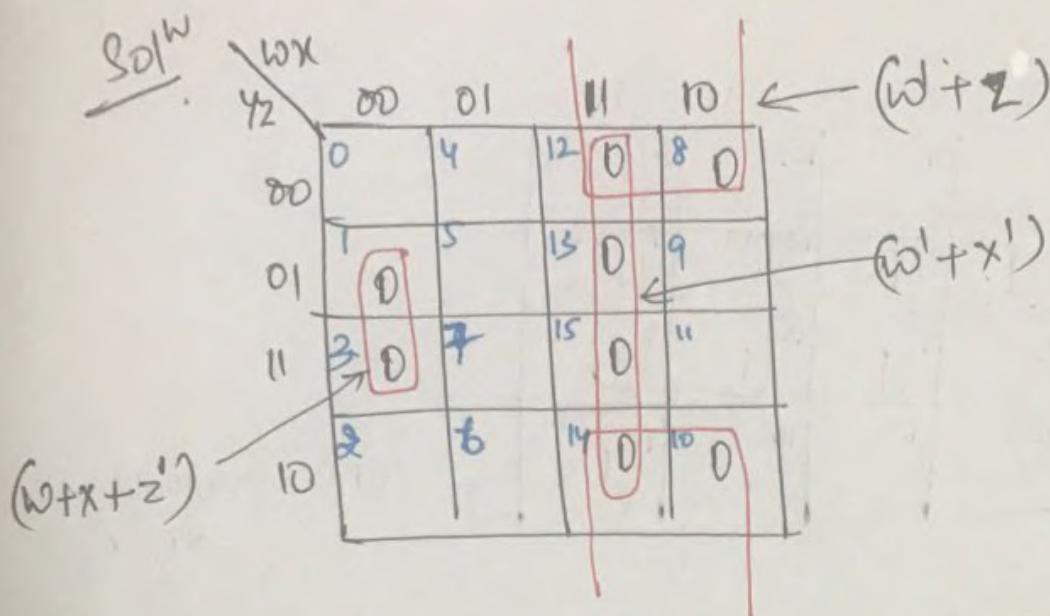

$$T = f(w, x, y, z) = \pi(1, 3, 8, 10, 12, 13, 14, 15)$$

$$T = (w'+z) (w'+x') (w+x+z')$$

(15)

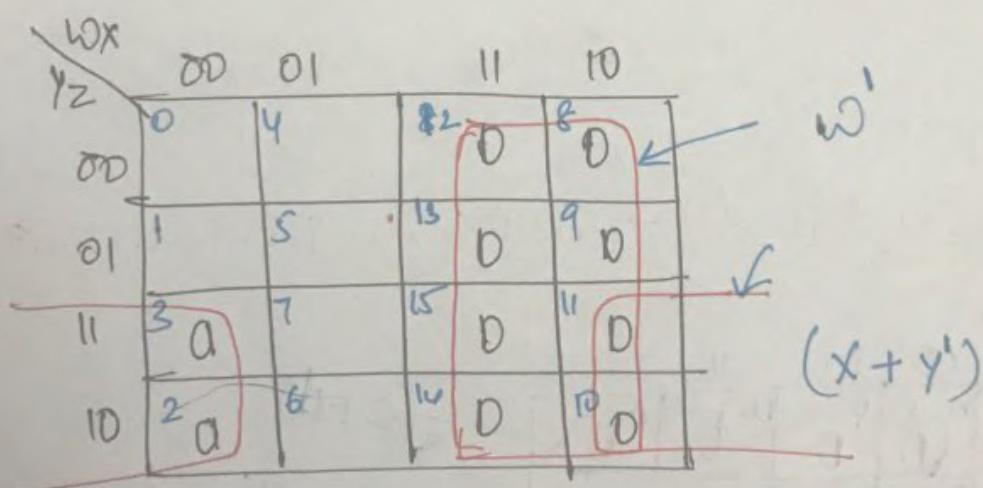

$$A = f(w, x, y, z) = \pi(2, 3, 8, 9, 10, 11, 12, 13, 14, 15)$$

$$A = w' \cdot (x+y')$$

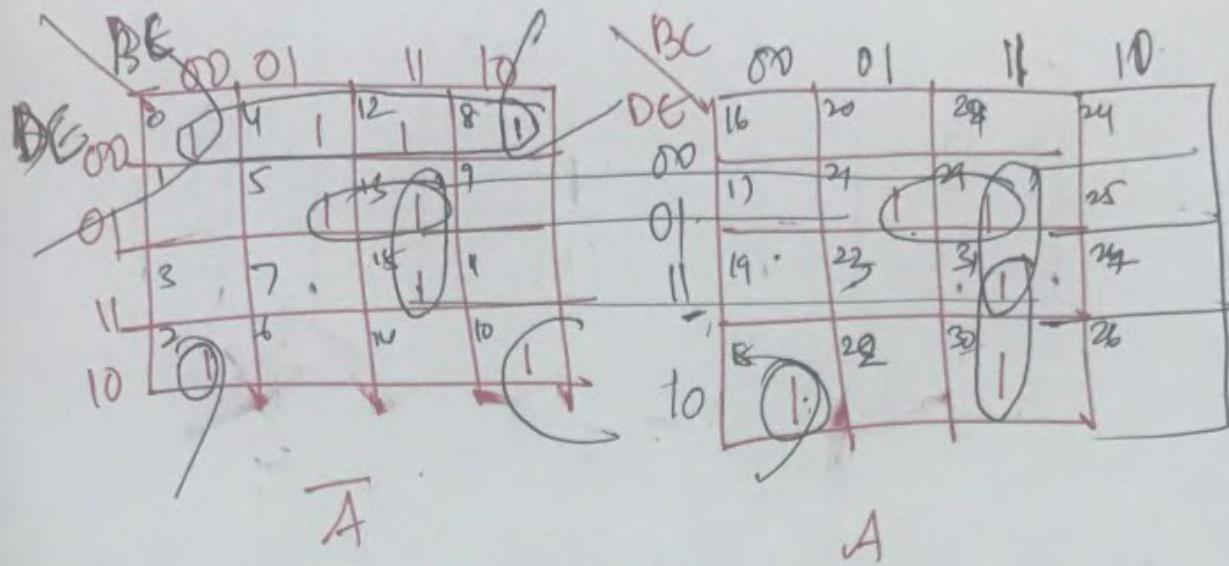

1b Simplify the following 5-variable expression using a K-map.

$$T = f(a, b, c, d, e) = \sum (0, 2, 8, 10, 16, 18, 24, 26)$$

- corners in a 4-variable map are logically adjacent.

- cut the 5-variable map in the centre and slide the right half over on top of the left, we can see that 4-variable maps aligned vertically.

- The square of one 4-variable map is logically adjacent to the square in the same relative position on the four variable map.

- Minterm  $\{0\}$  is vertically aligned with minterm  $\{16\}$ . All by minterms  $\{2, 18\}$ ,  $\{8, 24\}$  and  $\{10, 26\}$  are vertically aligned.

- Minterms located in all corners of each four variable map produces an EPI  $T = c'e'$ .

XX- The centres of the 2, 4-variable maps are also logically adjacent by the same reasoning.

(M)

SOLW.

$$R = xz$$

18)  $w = f(a, b, c, d, e) = \sum(1, 3, 4, 6, 9, 11, 12, 14, 17, 19, 20, 22, 25, 27, 28, 30)$

SOL

$$w = ce' + ce$$

|     |     |     |     |

|-----|-----|-----|-----|

| 100 | 001 | 011 | 110 |

| 01  | 1   | 1   | 1   |

| 11  | 1   | 1   | 1   |

9)

J = f(v, w, x, y, z) = \sum(4, 5, 6, 7, 9, 11, 13, 15, 25, 27, 29, 31)

SOL

$$J = wz + wz'$$

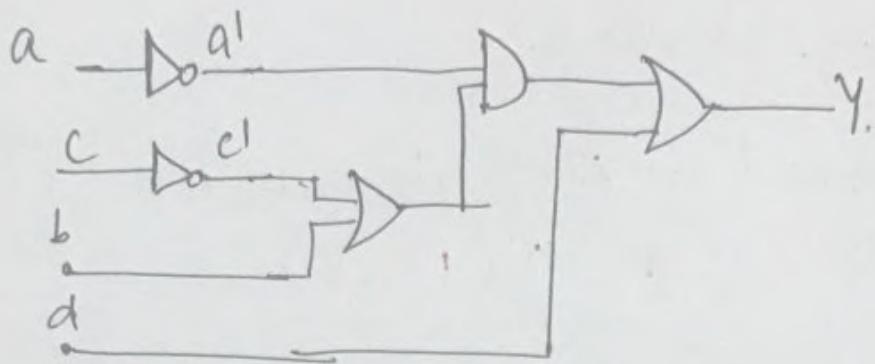

$$Y = a'(c c' + b) + d$$

Q2

Write the truth-table and design a circuit to generate op using K-map for the problem statement given.

Jan 2017

6M

→ op of a combinational circuit having 4 inputs and an op becomes logical 1 when two or more inputs gets logical 1.

Sol<sup>n</sup>

|    | a | b | c | d | Y |

|----|---|---|---|---|---|

| 0  | 0 | 0 | 0 | 0 | 0 |

| 1  | 0 | 0 | 0 | 1 | 0 |

| 2  | 0 | 0 | 1 | 0 | 0 |

| 3  | 0 | 0 | 1 | 1 | 1 |

| 4  | 0 | 1 | 0 | 0 | 0 |

| 5  | 0 | 1 | 0 | 1 | 1 |

| 6  | 0 | 1 | 1 | 0 | 1 |

| 7  | 0 | 1 | 1 | 1 | 1 |

| 8  | 1 | 0 | 0 | 0 | 0 |

| 9  | 1 | 0 | 0 | 1 | 1 |

| 10 | 1 | 0 | 1 | 0 | 1 |

| 11 | 1 | 0 | 1 | 1 | 1 |

| 12 | 1 | 1 | 0 | 0 | 1 |

| 13 | 1 | 1 | 0 | 1 | 1 |

| 14 | 1 | 1 | 1 | 0 | 1 |

| 15 | 1 | 1 | 1 | 1 | 1 |

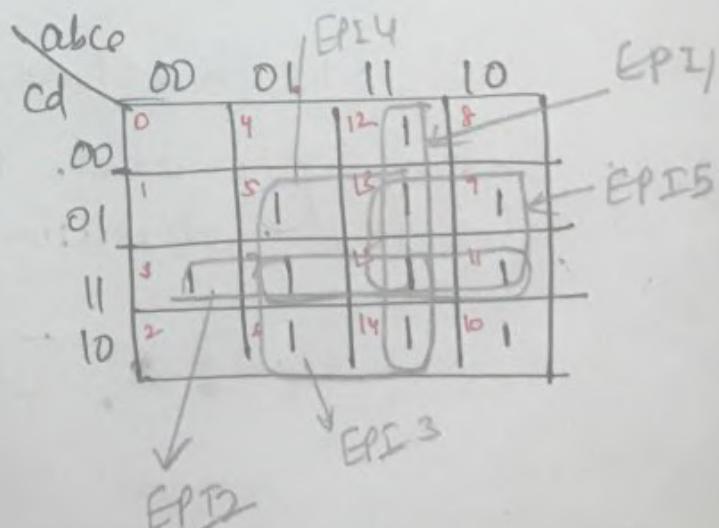

$$Y = \sum(3, 5, 6, 7, 9, 10, 11, 12, 13, 14, 15)$$

$$Y = ab + cd + bc + bd + ad$$

23

Jan 2017

14 Marks

obtain a minimal logical expression for the given maxterm expression using K-map.

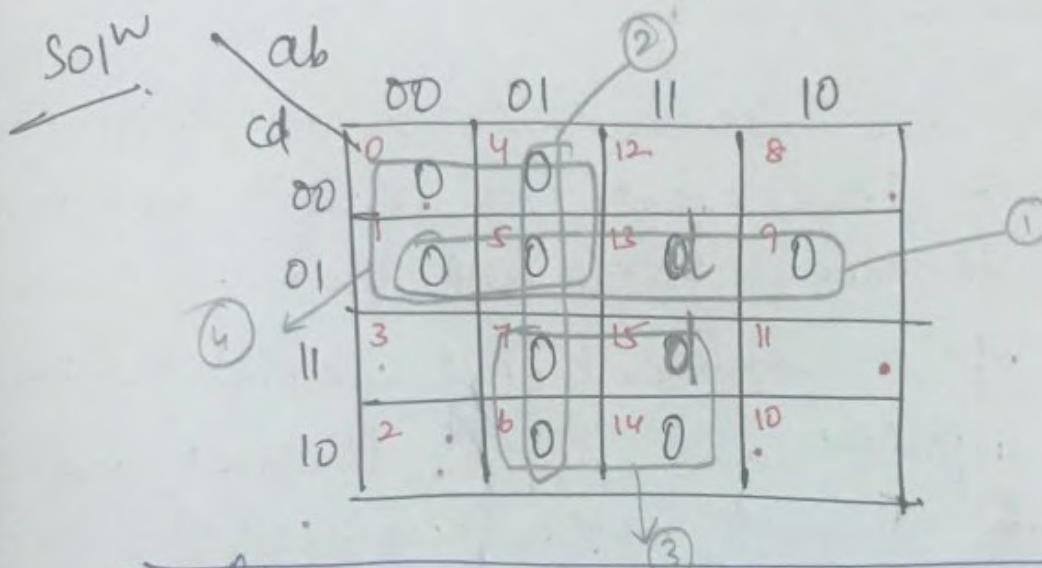

$$f(a, b, c, d) = \pi(0, 1, 4, 5, 6, 7, 9, 14) + \pi(13, 15)$$

$$f(a, b, c, d) = (c + d')(a + b')(b' + c')(a + c)$$

24

Use 2M method of minimization to obtain PIs and Minimal expression for the following minterm expression.

Jan 2017

8 M

$$f'(a, b, c, d) = \sum(0, 1, 4, 5, 7, 8, 13, 15) + \overline{d}(2)$$

0  $\rightarrow$  0000

Group 0

1  $\rightarrow$  0001

4  $\rightarrow$  0100

5  $\rightarrow$  0010

8  $\rightarrow$  1000

5  $\rightarrow$  0101

Group 2

7  $\rightarrow$  0111

13  $\rightarrow$  1110

Group 3

15  $\rightarrow$  1111

Group 4

| group | minterm | abcd |

|-------|---------|------|

| 0     | 0/      | 0000 |

| 1     | 1/      | 0001 |

|       | 2/      | 0010 |

|       | 3/      | 0000 |

| 2     | 5/      | 0101 |

| 3     | 7/      | 0111 |

|       | 6/      | 1101 |

| 4     | 15/     | 1111 |

Table 1: Minterm group of 2.

| group | minterm | abcd |

|-------|---------|------|

| 0     | (0,1)✓  | 000- |

|       | (0,2)✓  | 00-0 |

|       | (0,4)✓  | 0-00 |

|       | (0,8)✓  | -000 |

| 1     | (1,2)✓  | 0-01 |

|       | (1,3)✓  | 010- |

| 2     | (2,3)✓  | 01-1 |

|       | (2,4)✓  | -101 |

| 3     | (4,15)✓ | -111 |

|       | (5,15)✓ | 11-1 |

Table 2: Minterm group of 2.

Table 3: Minterm Groups of tr.

Q25 convert the boolean function to .

(a)  $Y = f(a, b, c) = (a+b)(a+c)$  minterm.

canonical form.

$$\begin{aligned} Y = f(a, b, c) &= (a+b) (a+c) \\ &= aa + ac + ba + bc \\ &= a + ac + ba + bc. \end{aligned}$$

$$\begin{aligned} Y = f(a, b, c) &= a(b+\bar{b})(c+\bar{c}) + ac(b+\bar{b}) \\ &\quad + ba(c+\bar{c}) + bc(a+\bar{a}) \end{aligned}$$

$$\begin{aligned} &= \cancel{abc} + \cancel{ab\bar{c}} + \cancel{a\bar{b}c} + \cancel{a\bar{b}\bar{c}} + \cancel{abc} + \cancel{a\bar{b}c} \\ &\quad + \cancel{abc} + \cancel{ab\bar{c}} + \cancel{a\bar{b}c} + \cancel{a\bar{b}\bar{c}} \end{aligned}$$

$$\boxed{Y = abc + ab\bar{c} + a\bar{b}c + a\bar{b}\bar{c} + \bar{a}bc.}$$

(b)  $P = f(a, b, c, d) = (a+b)(b+c)(\bar{c}+a)$  maxterm

canonical form

$$\begin{aligned} P &= (a+b+c\bar{c})(b+c+a\bar{a}) + (a+b\bar{b}+\bar{c}) \\ &= \underbrace{(a+b+c)}_{(a+b+\bar{c})} \underbrace{(a+b+\bar{c})}_{(a+\bar{b}+\bar{c})} \underbrace{(a+b+c)}_{(a+\bar{b}+c)} (\bar{a}+b+c) \end{aligned}$$

$$\boxed{P = (a+b+c)(a+b+\bar{c})(\bar{a}+b+c)(a+\bar{b}+\bar{c})}$$

Table 3: Mintcem groups of 4.

P14

| Group | Mintcem        | a b c d |        |

|-------|----------------|---------|--------|

| 0     | (0, 1, 4, 5)   | 0 - 0 - | $a'c'$ |

|       | (0, 4, 1, 5)   | 0 - 0 - |        |

| 2     | (5, 7, 13, 15) | - 1 - 1 | $bd$   |

|       | (5, 13, 7, 15) | - 1 - 1 |        |

Table 3: Mintcem groups of 4.

## Prime Implicant Table

PIs 0 1 4 5 7 8 13 15

a'c' (0, 1, 4, 5)  $\times \times \times x$ bd (5, 7, 13, 15)  $x \times \times \times$

$$f(a, b, c, d) = a'c' + bd + \cancel{b'c'd'}$$

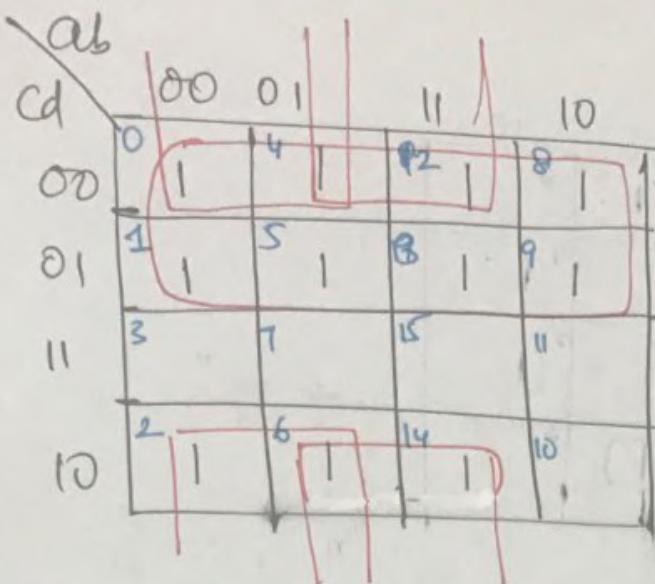

26) Find all the prime implicants of the function

$$f(a, b, c, d) = \pi(0, 2, 3, 4, 5, 12, 13) + \pi d(8, 10)$$

SDW

0  $\rightarrow$  0000

Group 0

2  $\rightarrow$  0010

4  $\rightarrow$  0100

8  $\rightarrow$  1000

10  $\rightarrow$  1010

12  $\rightarrow$  1100

13  $\rightarrow$  1101

15  $\rightarrow$  1111

13  $\rightarrow$  1101

Group 3.

Step 1: Arrange the maxterms in order of increasing no. of 1's

| Group | maxterm | abcd  |

|-------|---------|-------|

| 0     | 0       | 0000✓ |

| 1     | 2       | 0010✓ |

|       | 4       | 0100✓ |

|       | 8*      | 1000✓ |

| 2     | 3       | 0011✓ |

|       | 5       | 0101✓ |

|       | 10*     | 1010✓ |

|       | 12      | 1100✓ |

| 3     | 13      | 1101✓ |

Step 2: Grouping of maxterms of order 2

| Group | Maxterm    | abcd |

|-------|------------|------|

| 0     | (0, 2)✓    | 00-0 |

|       | (0, 4)✓    | 0-00 |

|       | (0, 8*)✓   | -000 |

| 1     | (2, 3) X   | 001- |

|       | (2, 10*)✓  | -010 |

|       | (4, 5)✓    | 010- |

|       | (4, 12)✓   | -100 |

|       | (8*, 10*)✓ | 10-0 |

|       | (8*, 12)✓  | 1-00 |

| 2     | (12, 13)✓  | 110- |

|       | (5, 13)✓   | -101 |

Step 3 : Maxterm grouping of order 4.

| Group | Maxterm                                   | abcd       |

|-------|-------------------------------------------|------------|

| 0     | (0, 2, 8 <sup>+</sup> , 10 <sup>+</sup> ) | -0-0 → b+d |

|       | (0, 4, 8 <sup>+</sup> , 12)               | --00 → c+d |

|       | (0, 8 <sup>+</sup> , 2, 10 <sup>+</sup> ) | -0-0 → b+d |

|       | (0, 8 <sup>+</sup> , 4, 12)               | --00 → c+d |

| 1     | (4, 5, 12, 13)                            | -10- b'+c  |

Step 4:

Prime Implicant Table.

| Group | Maxterm |     |   |   |     |     |       |                                |

|-------|---------|-----|---|---|-----|-----|-------|--------------------------------|

|       | 0       | 2   | 3 | 4 | 5   | 12  | 13    | 8 <sup>+</sup> 10 <sup>+</sup> |

| b+d   | x       | (x) |   |   |     |     |       | x (x)                          |

| c+d   |         | x   |   |   |     | (x) | x     | x                              |

| a+b+c |         |     | x |   | (x) |     |       |                                |

| b'+c  |         |     |   | x | (x) | x   | x (x) |                                |

Prime Implicants are

(b+d), (c+d), (a+b+c) & (b'+c)

Simplified Boolean expression

$$M = (b+d) (a+b+c) (b'+c)$$

$$(c+d) \text{ or } (a+b+c) (b'+c)$$

~~Q3~~

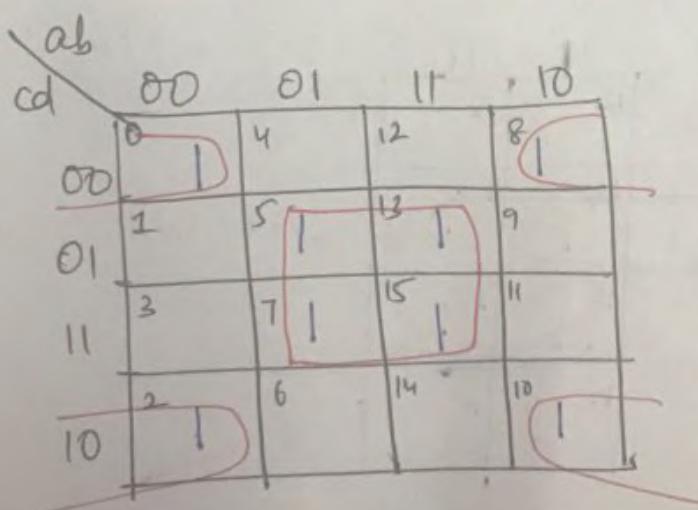

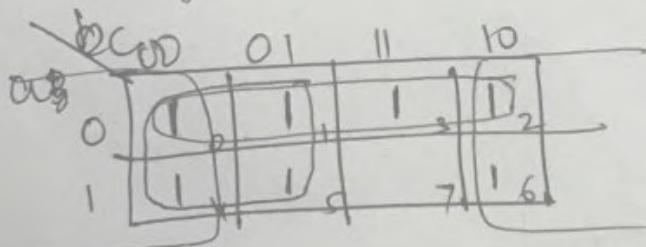

Verification using K-Map.

$$f(a, b, c, d) = \overline{\Pi}(0, 2, 3, 4, 5, 12, 13)$$

$$\overline{\Pi} d(8, 10)$$

| ab\cd | 00 | 01 | 11 | 10 |

|-------|----|----|----|----|

| 00    | 0  | 0  | 12 | 8  |

| 01    | 1  | 5  | 13 | 9  |

| 11    | 2  | 7  | 15 | 11 |

| 10    | 3  | 6  | 14 | 10 |

Handwritten annotations: The K-map shows minterms 0, 1, 2, 3, 5, 12, 13, and 15. Regions are circled and labeled: (0, 1) is labeled ①, (2, 3) is labeled ③, (5, 12, 13) is labeled ②, and (14, 15) is labeled ④. The term  $\overline{\Pi} d(8, 10)$  is written above the K-map, with a '+' sign above the 8 and 10. The variable  $d$  is circled in the 8 and 10 positions.

$$M = (b+d) (\overline{b}+c) (a+b+\overline{c})$$

21) Using k-map determine the minimal sum of product expression and realize the simplified expression using NAND gates

Jun 2017 (8m) P16

$$M = f(w, x, y, z) = \sum(1, 4, 5, 6, 11, 12, 13, 14, 15)$$

$$M = w'y'z + \bar{x}z' + wx + w'yz$$

$$M = z(wy + w'y') + x(z' + w)$$

Q8 Simplify the given boolean function using Quine-Mccluskey Method. Verify the result using K-map

June 2013

(12M)

$$Y = f(a, b, c, d) = \sum(0, 2, 3, 5, 8, 10, 11)$$

Soln

| Group | Minterm | a b c d |

|-------|---------|---------|

| 0     | 0       | 0 0 0 0 |

| 1     | 2       | 0 0 1 0 |

|       | 8       | 1 0 0 0 |

| 2     | 3       | 0 0 1 1 |

|       | 5       | 0 1 0 1 |

|       | 10      | 1 0 1 0 |

| 3     | 11      | 1 0 1 1 |

Table 1: Minterm Groups of 1.

- Arranging minterms in increasing order of no. of 1's.

Group 0  $\rightarrow$  0 1's      Group 2  $\rightarrow$  2 1's

Group 1  $\rightarrow$  1 1's      Group 3  $\rightarrow$  3 1's

Table 2: Minterm groups of two.

| group | Minterm    | abcd      |

|-------|------------|-----------|

| 0     | (0, 2) ✓   | 00 - 0 ✓  |

|       | (0, 8) ✓   | - 000 ✓   |

| 1     | (2, 3) ✓   | 0 01 - ✓  |

|       | (2, 10) ✓  | - 01 0 ✓  |

|       | (8, 10) ✓  | 1 0 - 0 ✓ |

| 2     | (3, 11) ✓  | - 011 ✓   |

|       | (10, 11) ✓ | 1 0 1 - ✓ |

Table 3: group of minterms of order 4.

| Group | Minterm        | ab cd   |

|-------|----------------|---------|

| 0     | (0, 2, 8, 10)  | - 0 - 0 |

|       | (0, 8, 2, 10)  | - 0 - 0 |

| 1     | (2, 3, 10, 11) | - 0 1 - |

|       | (2, 10, 3, 11) | - 0 1 - |

Table 4: creation of PI table

| PI   | Minterm        | 0 | 2 | 3 | 5 | 8 | 10 | 11 |

|------|----------------|---|---|---|---|---|----|----|

| b'd' | (0, 2, 8, 10)  | x | x |   |   | x |    |    |

| b'c  | (2, 3, 10, 11) |   | x | x |   |   | x  | x  |

a'b'c'd'

As 5 is not mapped to any PIs, it is added to the final expression.

$$\therefore Y = b'd' + b'c + a'b'c'd$$

Verification using K-map.

$$Y = b'd' + b'c + a'b'c'd$$

29) Find the minimal sum for the incomplete Boolean function using QM method & Prime Implicant to reduction.

$$f(a, b, c, d) = \sum (3, 4, 5, 7, 10, 12, 14, 15) + \sum d(2).$$

SOLW

|                       |

|-----------------------|

| 3 $\rightarrow$ 0011  |

| 5 $\rightarrow$ 0101  |

| 12 $\rightarrow$ 1100 |

| 10 $\rightarrow$ 1010 |

group 2

|                      |

|----------------------|

| 6 $\rightarrow$ 1000 |

| 2 $\rightarrow$ 0010 |

Group 1

|                       |

|-----------------------|

| 7 $\rightarrow$ 0111  |

| 14 $\rightarrow$ 1110 |

group 3

|                       |

|-----------------------|

| 15 $\rightarrow$ 1111 |

|-----------------------|

Group 4

Step 1: Arrange the minterms in increasing order of no. of 1's.

| Group | Minterm | abcd |

|-------|---------|------|

| 1     | 2*      | 0010 |

|       | 4       | 0100 |

| 2     | 3       | 0011 |

|       | 5       | 0101 |

|       | 12      | 1100 |

| 3     | 10      | 1010 |

|       | 7       | 0111 |

| 4     | 14      | 1110 |

|       | 15      | 1111 |

Step 2: Minterms of order 2.

| Group | Minterm               | abcd    |   |

|-------|-----------------------|---------|---|

| 1     | (2 <sup>4</sup> , 3)  | 001 - x | Q |

|       | (4, 5)                | 010 - x | R |

|       | (4, 12)               | -100 x  | S |

|       | (2 <sup>4</sup> , 10) | -010 x  | T |

| 2     | (3, 7)                | 0 -11 x | U |

|       | (5, 7)                | 01 -1 x | V |

|       | (12, 14)              | 11 -0 x | W |

|       | (10, 14)              | 1 -10 x | X |

| 3     | (7, 15)               | -11 1 x | Y |

|       | (14, 15)              | 111 - x | Z |

Step 3 : Grouping of minterms of order 4.

| Group | Minterm      | abcd |

|-------|--------------|------|

| 1     | NOT POSSIBLE |      |

(P19)

Step 4 : Peirce Implicant Table.

↓

Don't care

| rows | PI                | 2 <sup>4</sup> | 3 | 4 | 5 | 7 | 10 | 12 | 14 | 15 | ... |

|------|-------------------|----------------|---|---|---|---|----|----|----|----|-----|

| Q    | $\bar{a}\bar{b}c$ | x              | x |   |   |   |    |    |    |    | ... |

| R    | $\bar{a}b\bar{c}$ |                |   | x | x |   |    |    |    |    | ... |

| S    | $b\bar{c}\bar{d}$ |                |   | x |   |   |    |    | x  |    | ... |

| T    | $\bar{b}c\bar{d}$ | x              |   |   |   |   |    | x  |    |    | ... |

| U    | $\bar{a}\bar{b}d$ |                | x |   |   | x |    |    |    |    | ... |

| V    | $\bar{a}bd$       |                |   | x |   | x |    |    |    |    | ... |

| W    | $ab\bar{c}$       |                |   |   |   |   | x  | x  |    |    | ... |

| X    | $a\bar{b}\bar{d}$ |                |   |   |   | x |    |    | x  |    | ... |

| Y    | $bcd$             |                |   |   | x |   |    |    | x  |    | ... |

| Z    | $abc$             |                |   |   |   |   | x  | x  | x  | x  | ... |

$$Y = f(A B C D E) = \sum (1, 5, 6, 7, 9, 13, 14, 15, 16, 19, 24, 30, 31)$$

(P2)

$$A = 0 (\bar{A})$$

$$A = 1$$

$$Y = \bar{A} \bar{D} E + \underline{A} \bar{B}' \bar{C}' D E + \underline{\bar{A} \bar{C} \bar{D} \bar{E}} + B C D + \bar{A} \bar{C} D$$

$$f(A B C D E) = \sum m(2, 3, 4, 6, 11, 12, 14, 17, 18, 20, 22, 25, 28, 30)$$

$$Y = \underline{\bar{C} \bar{E}} + \bar{A} \bar{C} D E + A \bar{C} D E + \bar{B} D \bar{E} + \underline{\bar{C} \bar{D} \bar{E}}$$

③  $f(ABCDE)$

$$f = \overline{A}\overline{C}\overline{E} + \overline{A}\overline{B}\overline{C} + \overline{B}\overline{C}$$

$$f = \overline{A}\overline{E}\overline{C} + \overline{A}\overline{D}\overline{E} + \overline{D}\overline{E}\overline{B}\overline{C} + \overline{A}\overline{D}\overline{B}\overline{C} +$$

~~$+ \overline{C}\overline{D}\overline{E}$~~

~~$+ \overline{B}\overline{E}\overline{C}$~~

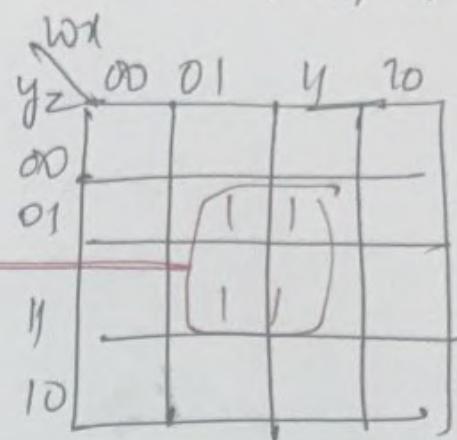

④  $R = f(wxyz) = \sum_{m=5,7,13,15,21,23,29,31}$

$\bar{V}$  $\checkmark$

$$R = zx$$

⑨ Second Method

$\bar{V}$  $\checkmark$

$$J = wz + \bar{v} \bar{w} x$$

~~z~~

① Obtain all the prime implicants of the given Boolean functions using Quine-McCluskey method. (25)

$$(1) f(abc) = \sum m(0, 2, 3, 4)$$

|  |  | bc | 00 | 01 | 11 | 10 |                                       |

|--|--|----|----|----|----|----|---------------------------------------|

|  |  | a  | 0  | 1  | 1  | 1  |                                       |

|  |  | 0  | 1  | 0  | 1  | 1  | $y = \bar{b}\bar{c} + \bar{a}\bar{b}$ |

|  |  | 1  | 0  | 1  | 1  | 0  | Ans                                   |

$$PI (0, 4) \rightarrow \bar{b}\bar{c} \rightarrow EPI$$

$$PI (2, 3) \rightarrow \bar{a}\bar{b} \rightarrow EPI$$

$$PI (0, 2) \rightarrow \bar{a}\bar{c} \rightarrow PI$$

|   | abc | y |

|---|-----|---|

| 0 | 000 | 1 |

| 1 | 001 | 0 |

| 2 | 010 | 1 |

| 3 | 011 | 1 |

| 4 | 100 | 1 |

| 5 | 101 | 0 |

| 6 | 110 | 0 |

| 7 | 111 | 0 |

Group of 0-1's  $\rightarrow 000 \rightarrow 0$  ✓

Group of 1-1's  $\rightarrow 001 \rightarrow 1$

$010 \rightarrow 2$  ✓

$100 \rightarrow 4$  ✓

Group of 2-1's  $011 \rightarrow 3$  ✓

$101 \rightarrow 5$

$110 \rightarrow 6$

Group of 3-1's  $111 \rightarrow 7$

① Grouping minterms according to no. of 1's

| Group | Minterm | abc     |

|-------|---------|---------|

| 0     | 0       | 000     |

| 1     | 2 4     | 010 100 |

| 2     | 3       | 011     |

Table 2 : creation of minterms groups of 2

| group | minterm | abc |

|-------|---------|-----|

| 0     | 0, 2    | 0-0 |

|       | 0, 4    | -00 |

| 1     | 2, 3    | 01- |

| PI terms<br><del>minterm</del> | Decimal | 0 | 2 | 3 | 4 |

|--------------------------------|---------|---|---|---|---|

| $\bar{a}\bar{c}$               | 0, 2    | X | X |   |   |

| $\bar{b}\bar{c}$               | 0, 4    | X |   |   | X |

| $\bar{a}b$                     | 2, 3    |   | X | X |   |

$Y = \bar{a}b + \bar{b}\bar{c}$

②  $Y = f(abc) = \sum m(0, 1, 2, 3, 4, 5, 6)$

PI  $(0, 2, 4, 6) \rightarrow \bar{c}$

PI  $(0, 1, 4, 5) \rightarrow \bar{b}$

PI  $(0, 1, 2, 3) \rightarrow \bar{a}$

$$Y = \bar{a} + \bar{b} + \bar{c}$$

Group of 0-1's  $\rightarrow 000 \rightarrow 0^-$

Group of 1-1's  $\rightarrow 001 \rightarrow 2^-$

$010 \rightarrow 2^-$

$100 \rightarrow 4^-$

Group of 2-1's  $\rightarrow 011 \rightarrow 3^-$

$110 \rightarrow 6^-$

$101 \rightarrow 5^-$

# Creation of minterms of 2.

Q2

R2b

| Group | Minterm | abc | Grouping minterms according to no. of 1's |

|-------|---------|-----|-------------------------------------------|

| 0     | 0       | 000 |                                           |

| 1     | 1       | 001 |                                           |

|       | 2       | 010 |                                           |

|       | 4       | 100 |                                           |

| 2     | 3       | 011 |                                           |

|       | 5       | 101 |                                           |

|       | 6       | 110 |                                           |

# creation of minterms of 2

| Group | Minterm | abc |

|-------|---------|-----|

| 0     | 0,1     | 00- |

|       | 0,2     | 0-0 |

|       | 0,4     | -00 |

| 1     | 1,3     | 0-1 |

|       | 1,5     | -01 |

|       | 2,3     | 01- |

|       | 2,6     | -10 |

|       | 4,5     | 10- |

|       | 4,6     | 1-0 |

# creation of minterms of 4

| Group | Minterm | abc  |           |

|-------|---------|------|-----------|

| 0     | 0,1,2,3 | 0--- | $\bar{a}$ |

|       | 0,1,4,5 | -0-  | $\bar{b}$ |

|       | 0,2,4,6 | --0  | $\bar{c}$ |

| PI terms  | Decimal     | 0 | 1 | 2 | 3 | 4 | 5 | 6 |

|-----------|-------------|---|---|---|---|---|---|---|

| $\bar{A}$ | 0, 1, 2, 3, | X | X | X | X |   |   |   |

| $\bar{B}$ | 0, 1, 4, 5  | X | X |   | X | X |   |   |

| $\bar{C}$ | 0, 2, 4, 6  | X |   | X | X |   | X |   |

$$Y_2 = \bar{A} + \bar{B} + \bar{C}$$

# Solving POS Using QM technique.

P28

$$\textcircled{1} \quad Y = f(abc'd) = \overline{\text{M}}(0, 2, 3, 4, 5, 12, 13) + \overline{\text{M}}(8, 10)$$

Soln  $y = f(abc'd) = \overline{\text{M}}(0, 2, 3, 4, 5, 8^*, 10^*, 12, 13)$

$M_0 \ M_2 \ M_3 \ M_4 \ M_5 \ M_8 \ M_{10} \ M_{12} \ M_{13}$

$$y = M_0 \cdot M_2 \ M_3 \ M_5 \ M_8 \ M_{10} \ M_{12} \ M_{13}$$

$$\bar{y} = \overline{M_0 \ M_2 \ M_3 \ M_5 \ M_8 \ M_{10} \ M_{12} \ M_{13}}$$

$$\bar{y} = \cancel{M_0} \cdot m_0 + m_2 + m_3 + m_5 + m_8 + m_{10} + m_{12} + m_{13}$$

let us apply QM technique to find the Prime Implicants of  $\bar{y}$ .

Step 1: Arranging the minterms in order of no. of 1's.

Group 0  $\rightarrow 0000 \rightarrow 0$

Group 1  $\rightarrow 0010 \rightarrow 2$

$\rightarrow 1000 \rightarrow 8^*$

Group 2  $\rightarrow 0011 \rightarrow 3$

$0101 \rightarrow 5$

$1010 \rightarrow 10^*$

$1100 \rightarrow 12$

Group 3  $\rightarrow 1101 \rightarrow 13$

Step 2: Group of minterms in Ascending order

| Group | minterm       | abcd                       |

|-------|---------------|----------------------------|

| 0     | 0             | 0000 ✓                     |

| 1     | 2<br>8*       | 0010 ✓<br>1000 ✓           |

| 2     | 3<br>5<br>10* | 0011 ✓<br>0101 ✓<br>1010 ✓ |

| 3     | 12<br>13      | 1100 ✓<br>1101 ✓           |

Step 3: Group of minterms of 2

(P29) ②

| Group | Minterm   | abcd             |

|-------|-----------|------------------|

| 0     | (0, 2)    | 00-0 ✓           |

|       | (0, 8*)   | -000 ✓           |

| 1     | (2, 3)    | 001 - X          |

|       | (2, 10*)  | <del>010</del> ✓ |

|       | (8*, 10*) | <del>100</del> ✓ |

|       | (8*, 12)  | 1-00 X           |

| 2     | (5, 13)   | -101 X           |

|       | (12, 13)  | 110 - X          |

Step 4: Group of minterms of 4

| Group | Minterm          | abcd |

|-------|------------------|------|

| 0     | (0, 2), 8*, 10*  | -0-0 |

|       | (0, 8*) (2, 10*) | -0-0 |

| 1     |                  |      |

| P8 | (0 2 8* 10) | abcd  | → | Minterm | Maxterm             |

|----|-------------|-------|---|---------|---------------------|

|    |             |       |   | b' d'   | b+d                 |

|    | (2, 3)      | 001 - | → | a'b'c'  | a+b+c'              |

|    | (8*, 12)    | 1-00  | → | a'c'd'  | $\bar{a}+c+d$       |

|    | (5, 13)     | -101  | → | b'c'd*  | $\bar{b}+c+d$       |

|    | (12, 13)    | 110 - | → | abc'    | $\bar{a}+\bar{b}+c$ |

$y = (b+d)(a+b+c)(\bar{a}+c+d)(b+c+\bar{d})(\bar{a}+\bar{b}+c)$

②  $y = f(abcd) = \overline{\pi}(0, 2, 3, 4, 5, 12, 13) + \overline{dc}(8, 10)$

$$y = (a+b+\bar{c})(b+d)(c+d)(\bar{b}+c)$$

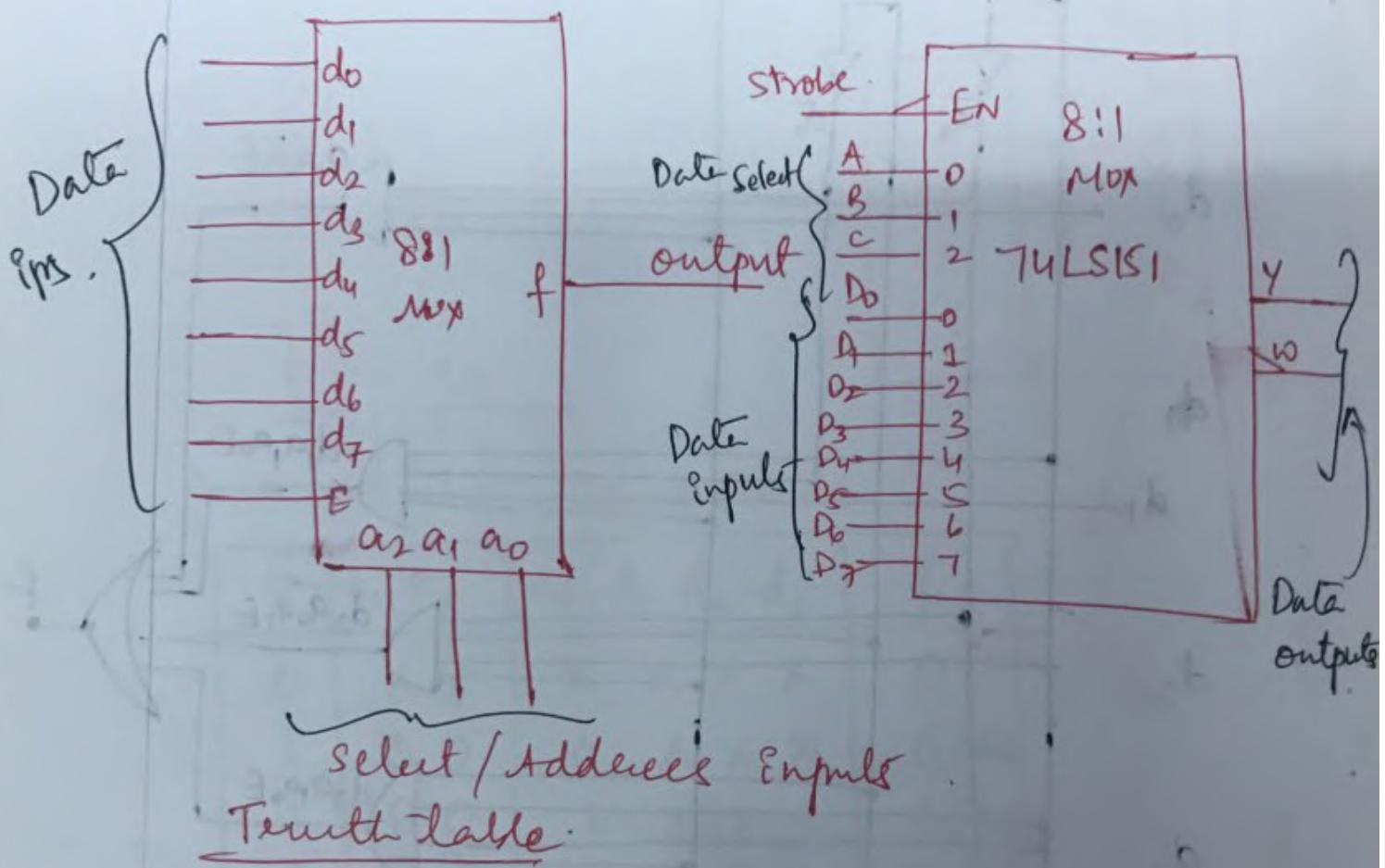

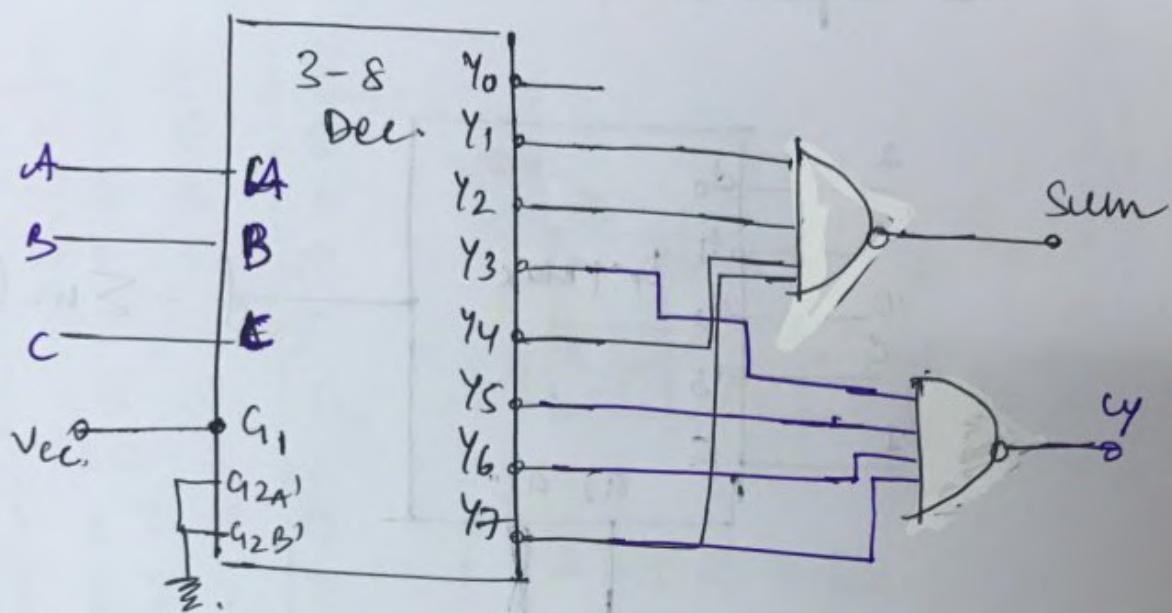

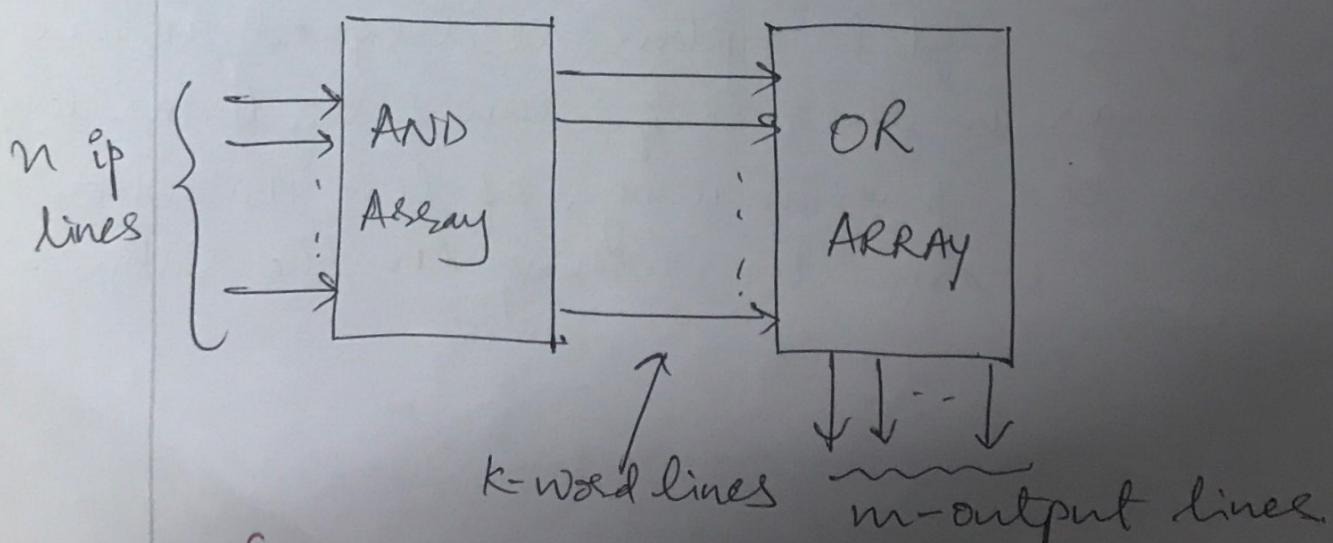

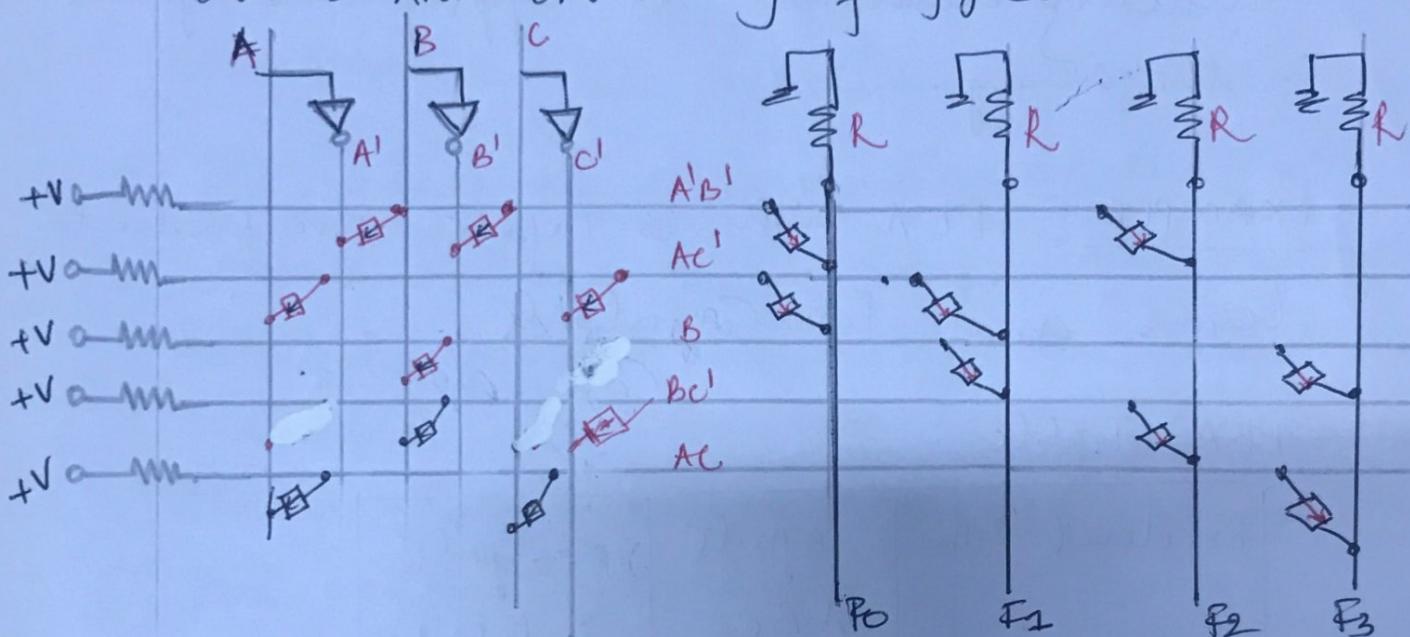

## MODULE 2: ANALYSIS AND DESIGN

### OF COMBINATIONAL LOGIC

- General approach to combinational logic design.

- Decoders

- (a) BCD Decoders

- Encoders

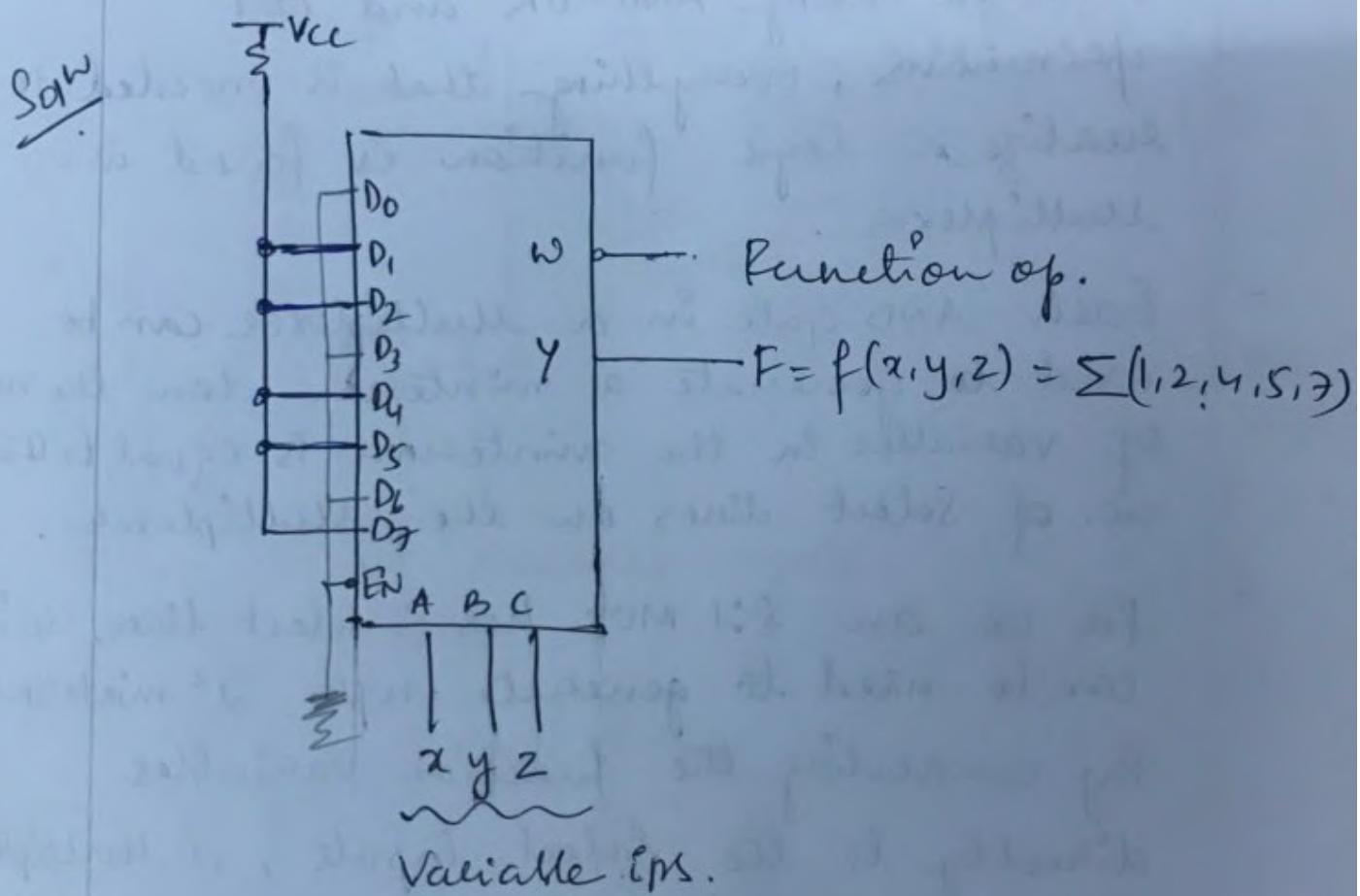

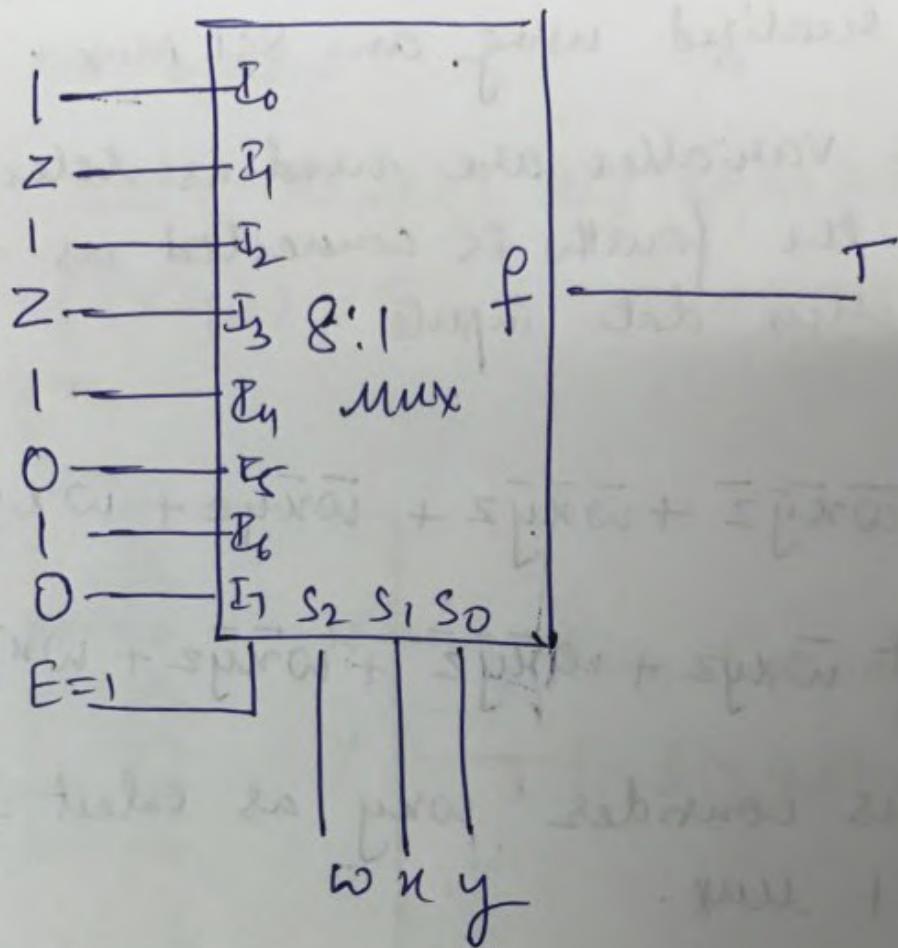

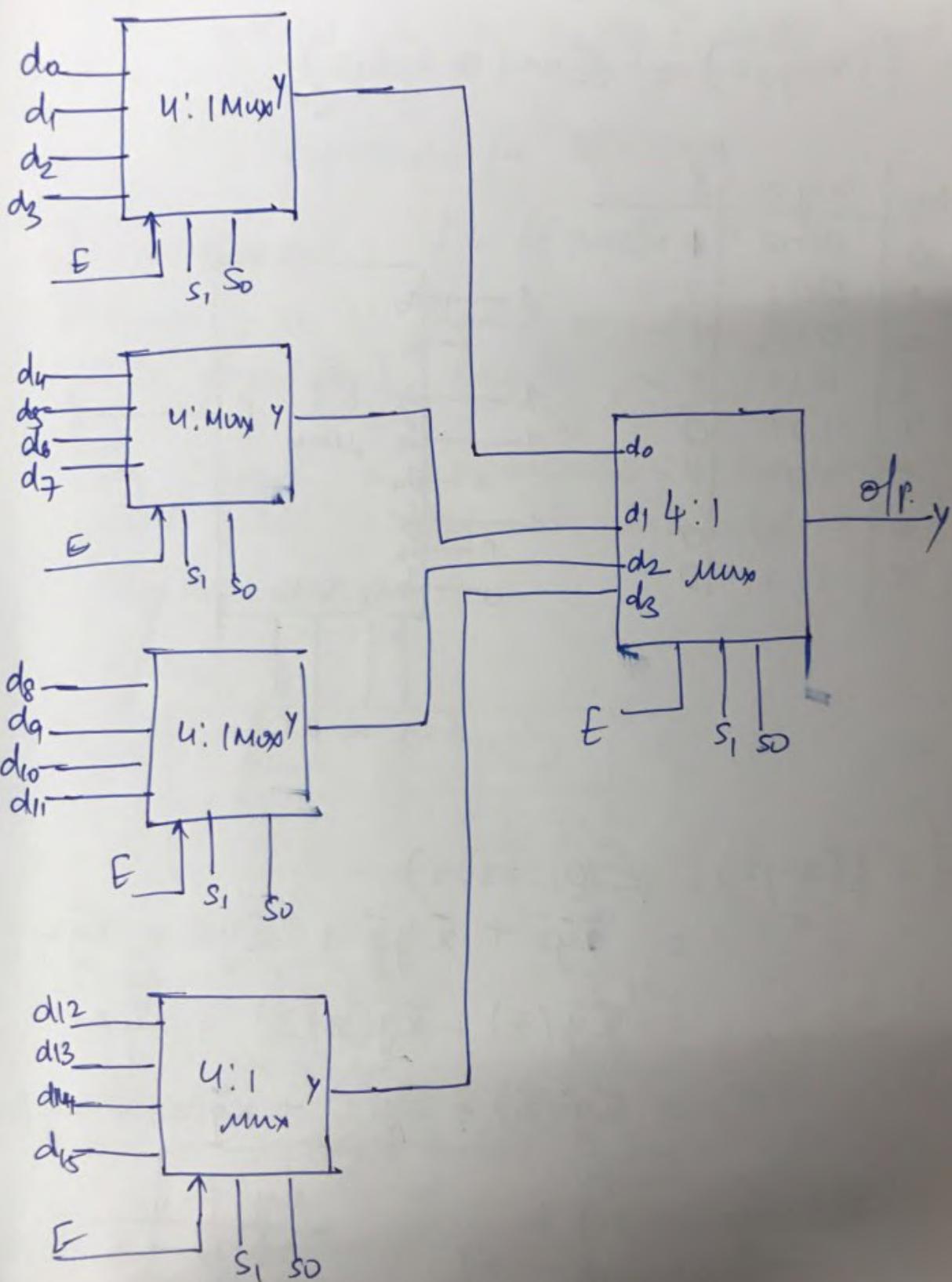

- Digital Multiplexers

- (a) Using Multiplexers as Boolean function generators.

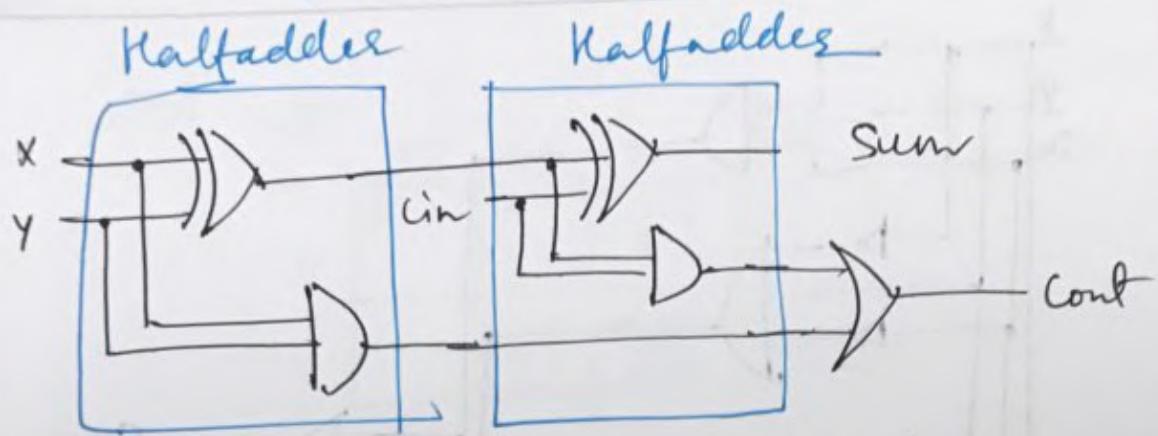

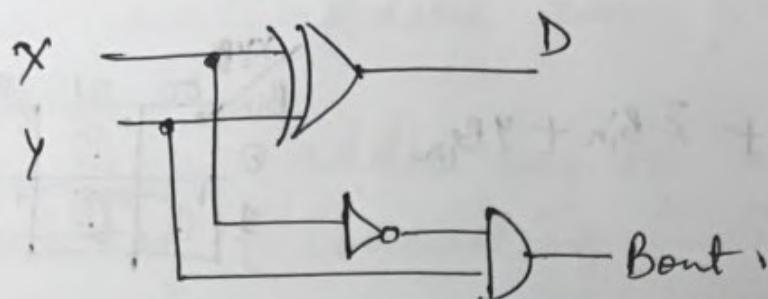

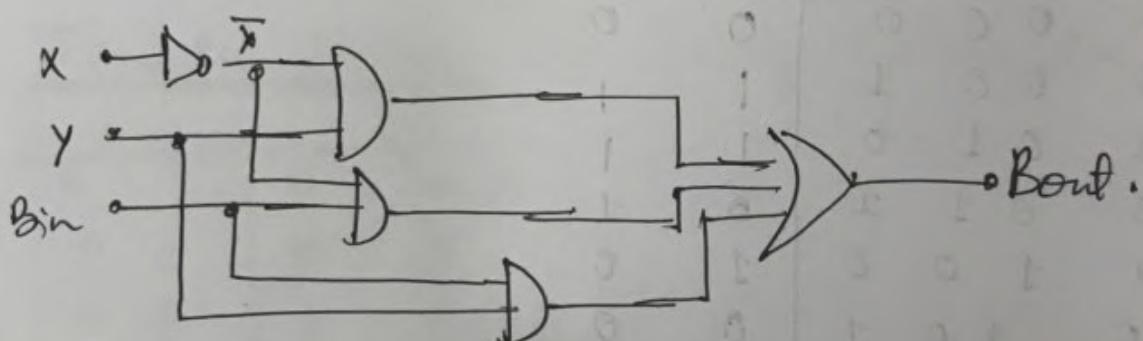

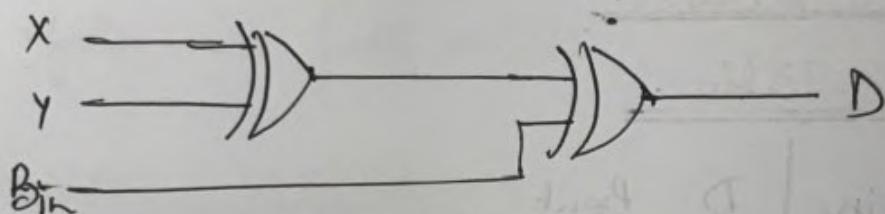

- Adders and Subtractors

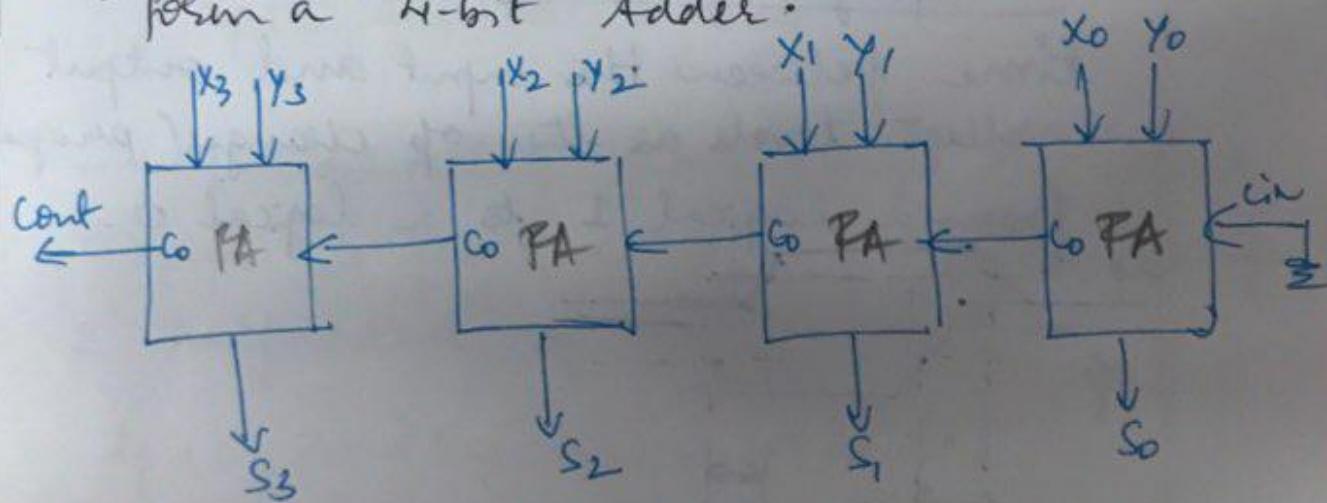

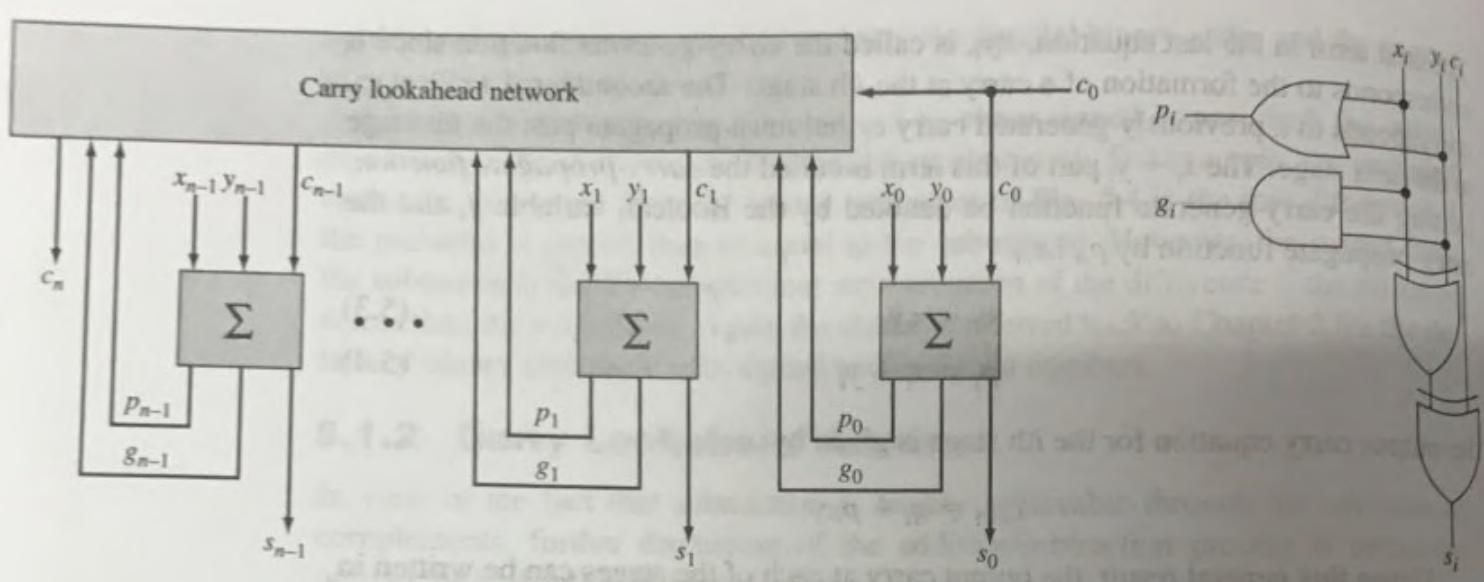

- (a) cascading full adders

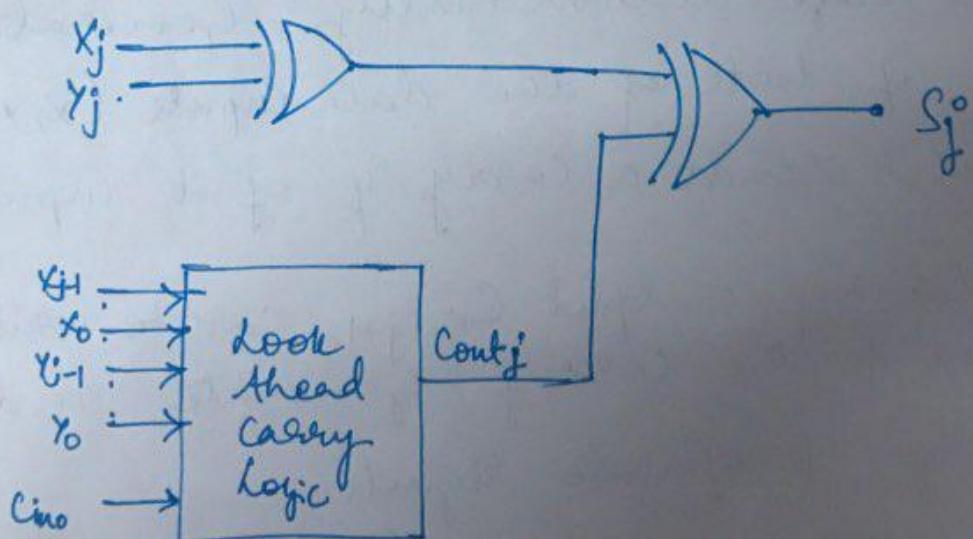

- (b) look ahead carry

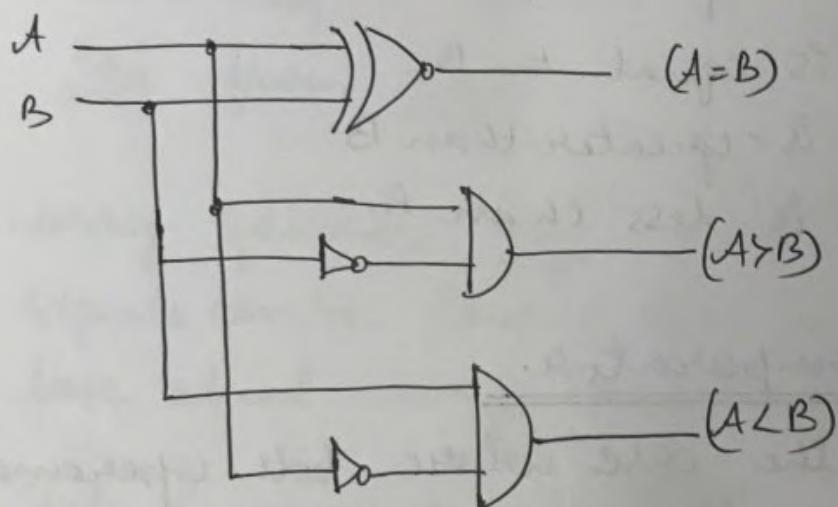

- Binary comparators.

III ECE

## General approach to combinational logic Design.

- The synthesis of combinational logic starts with a problem statement and progresses through a series of steps, terminating in the final circuit design.

- The combinational logic design steps are as follows.

Step 1 : Develop a statement describing the problem to be solved.

Step 2 : Based on the problem statement, construct a truth table that clearly establishes the relation b/w the input and output variables.

Step 3 : Use K-maps or QM Techniques to simplify the functions in deriving the output equations. This may require that the output equations be expressed as either SOP or POS. The best solution will require the fewest gates and gate inputs.

Step 4 : Arrange the simplified equations to suit the logic primitive type to be used in realizing the circuit. (using NANDS, NORs or AND-OR logic required)

Step 5 : Draw the final logic diagram.

Step 6 : Document the design by identifying variables names that indicate assertion levels, if possible provide Truth table.

Example: Design a combinational circuit that will multiply 2, 2-bit binary values.

Soln ① Let the inputs be  $A(A_1, A_0)$  &  $B(B_1, B_0)$ . and the output be  $P(P_3, P_2, P_1, P_0)$ .

- The four output variables are necessary because the maximum product of two, 2-bit values requires 4 bits. Let each variable be active high.

⑨ Construct the Truth table (Next page)

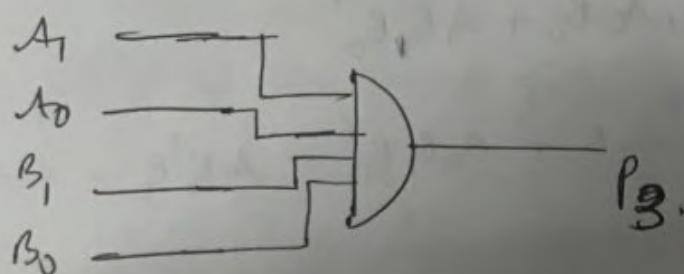

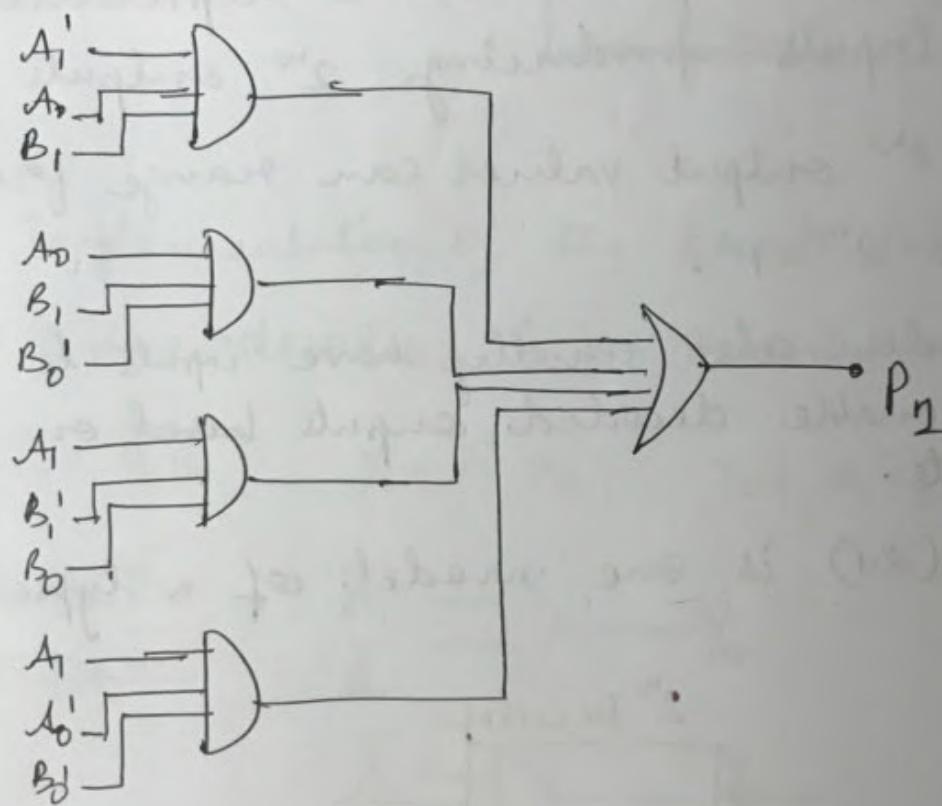

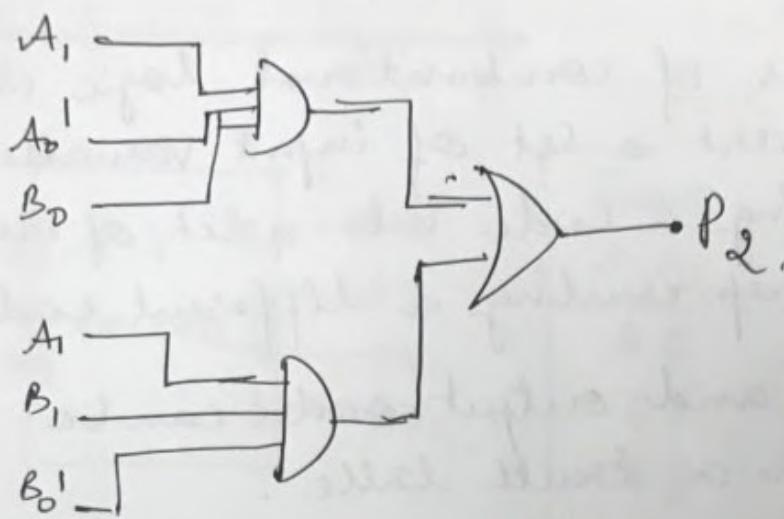

③ The individual simplified equations are:

$$P_3 = A_1 A_0 B_1 B_0.$$

$$P_2 = A_1 A_0' B_0 + A_1 B_1 B_0'$$

$$P_3 = A_1' A_0 B_1 + A_0 B_1 B_0' + A_1 B_0' + A_1 A_0' B_0$$

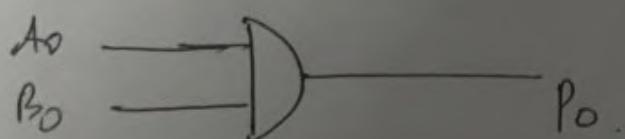

$$P_0 = A_0 B_0$$

Truth table

| $A_3 A_2 A_1 A_0$ | $P_3 P_2 P_1 P_0$ |

|-------------------|-------------------|

| 0 0 0 0           | 0 0 0 0           |

| 0 0 0 1           | 0 0 0 0           |

| 0 0 1 0           | 0 0 0 0           |

| 0 0 1 1           | 0 0 0 0           |

| 0 1 0 0           | 0 0 0 0           |

| 0 1 0 1           | 0 0 0 1           |

| 0 1 1 0           | 0 0 1 0           |

| 0 1 1 1           | 0 0 1 1           |

| 1 0 0 0           | 0 0 0 0           |

| 1 0 0 1           | 0 0 0 0           |

| 1 0 1 0           | 0 1 0 0           |

| 1 0 1 1           | 0 1 1 0           |

| 1 1 0 0           | 0 0 0 0           |

| 1 1 0 1           | 0 0 1 1           |

| 1 1 1 0           | 0 1 1 0           |

| 1 1 1 1           | 1 0 0 1           |

Logic Diagram for 2x2-bit Multiplier

## DECODERS.

- are a class of combinational logic circuits that convert a set of input variables representing a code into a set of output variables representing a different code.

- The input and output codes can be expressed in a truth table.

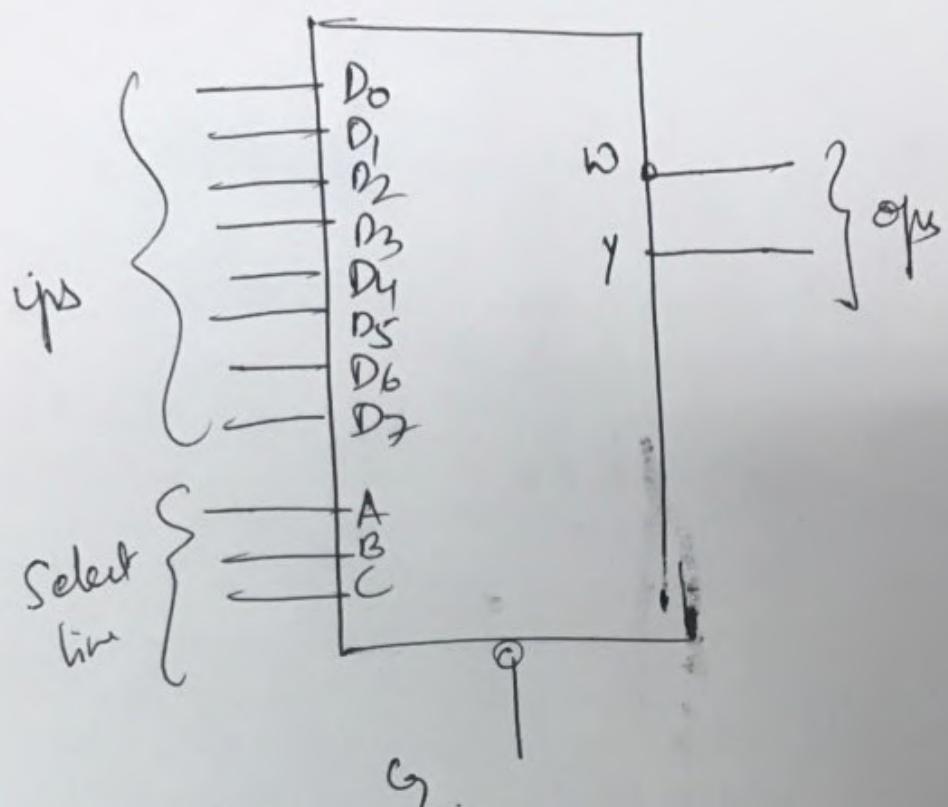

- Encoded information is represented as  $n$  inputs producing  $2^n$  outputs.

- The  $2^n$  output values can range from 0 to  $2^n - 1$ .

- Decoders also usually have inputs to activate or enable decoded outputs based on data inputs.

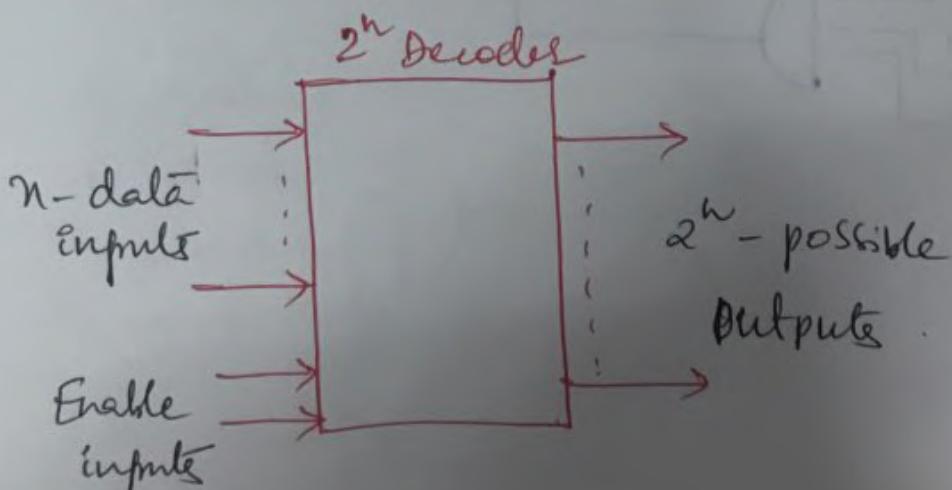

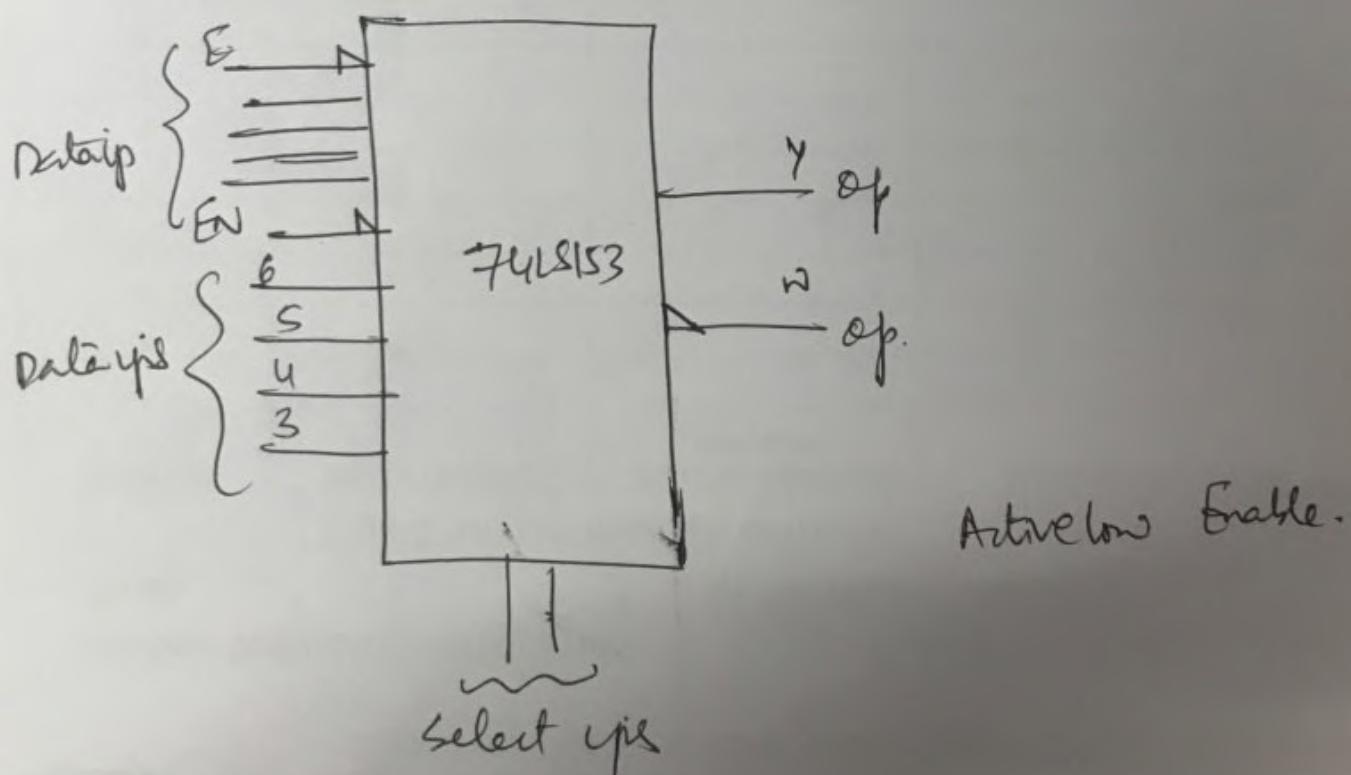

- Fig (2.1) is one model of a typical decoder.

fig 2.1 : Typical Decoder.

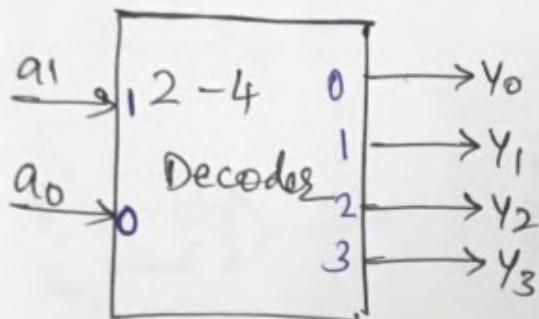

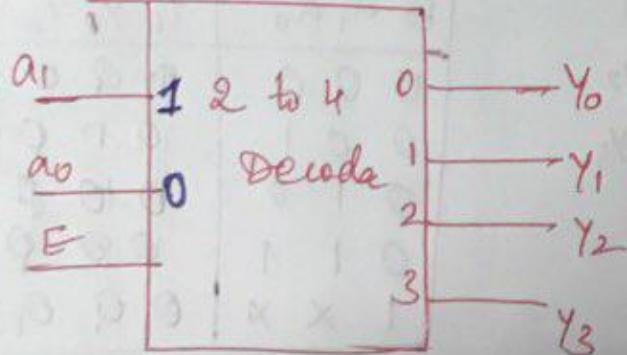

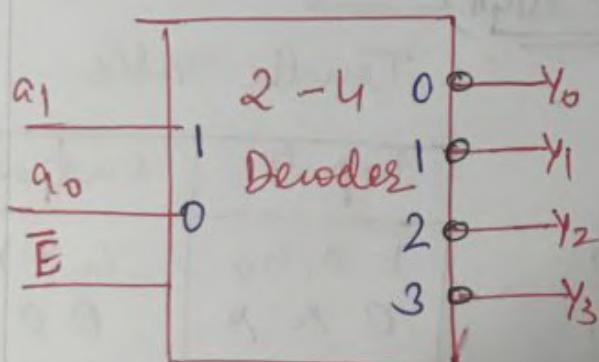

## 2-4 line DECODER

Truth Table

| Inputs     | Outputs                 |

|------------|-------------------------|

| $a_1, a_0$ | $y_0 \ y_1 \ y_2 \ y_3$ |

| 00         | 1 0 0 0                 |

| 01         | 0 1 0 0                 |

| 10         | 0 0 1 0                 |

| 11         | 0 0 0 1                 |

Symbol

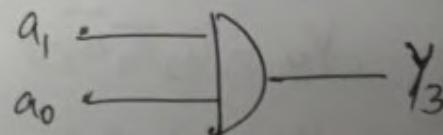

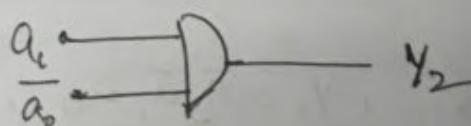

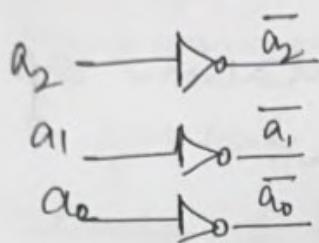

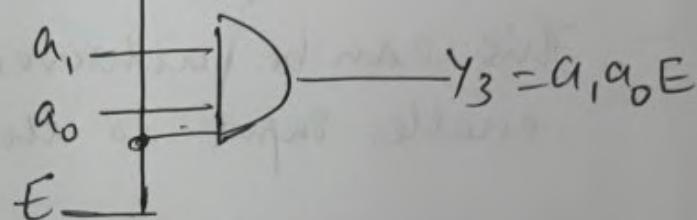

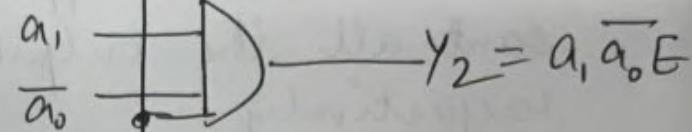

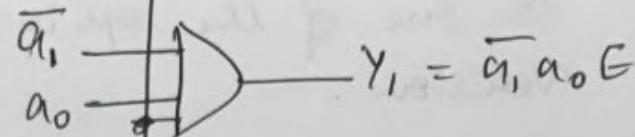

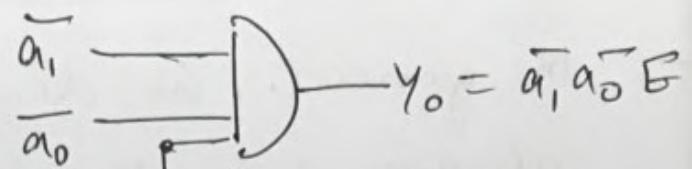

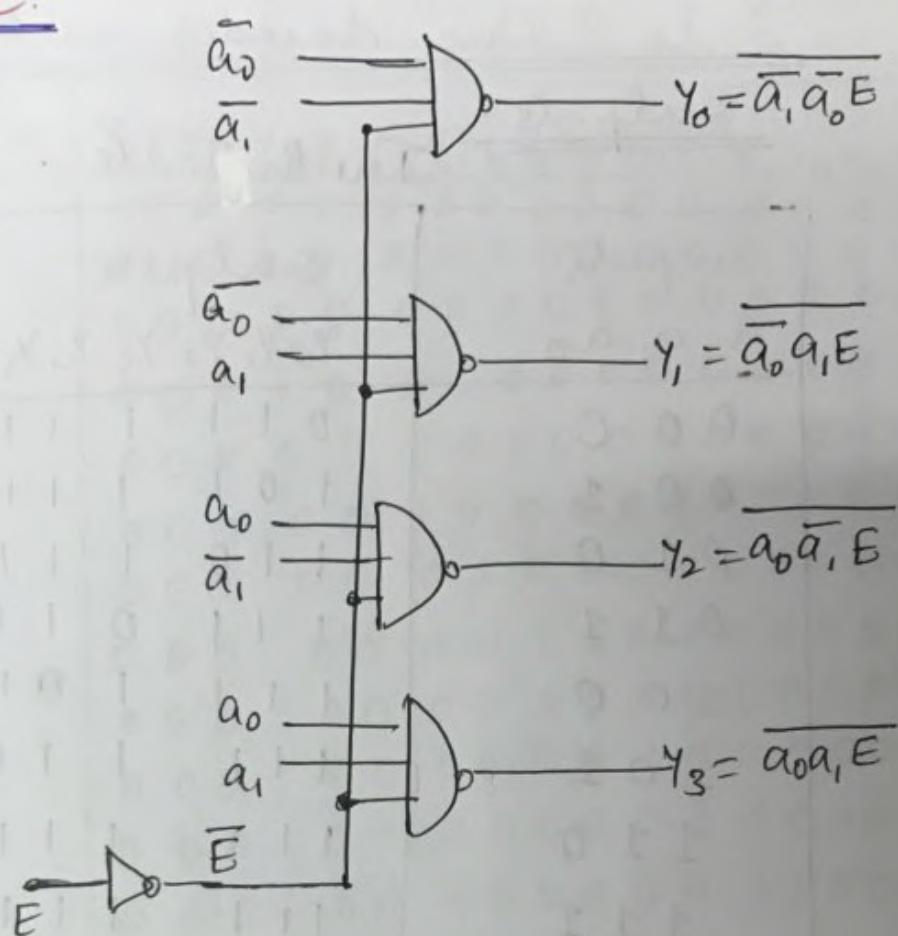

- The implementation of the truth table of the 2 to 4 line decoder is as shown.

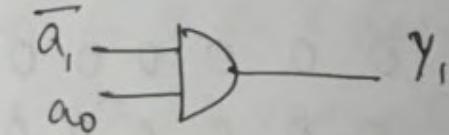

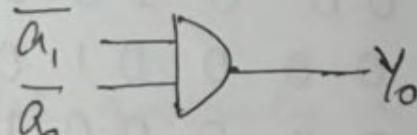

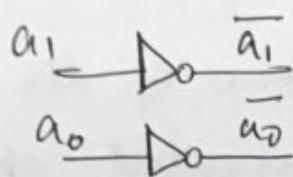

$$y_0 = \bar{a}_1 \bar{a}_0, \quad y_1 = \bar{a}_1 a_0, \quad y_2 = a_1 \bar{a}_0, \quad y_3 = a_1 a_0.$$

$$a_1 \rightarrow \bar{a}_1$$

$$a_0 \rightarrow \bar{a}_0$$

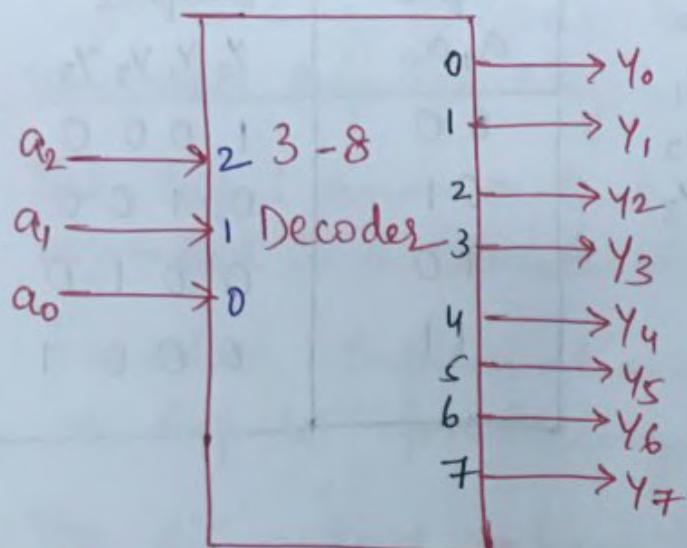

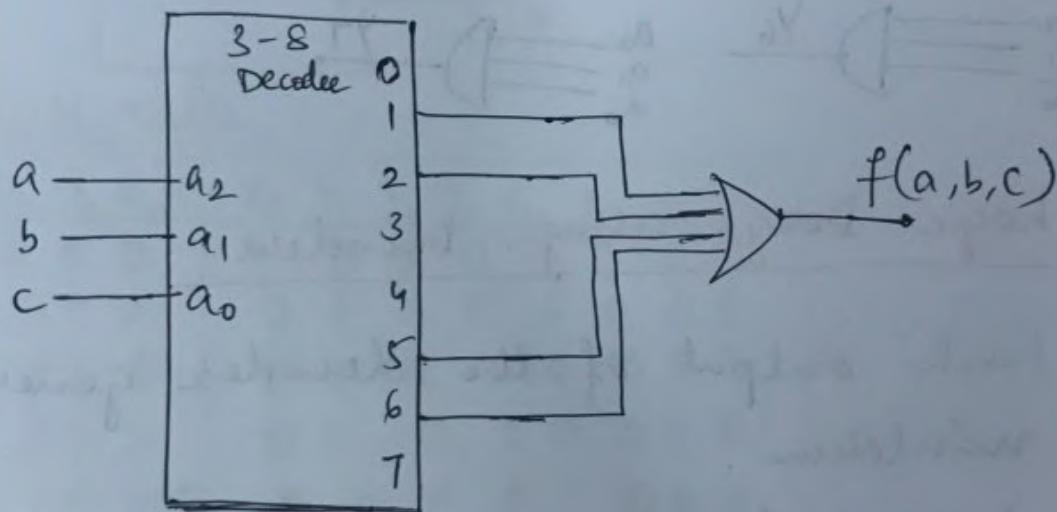

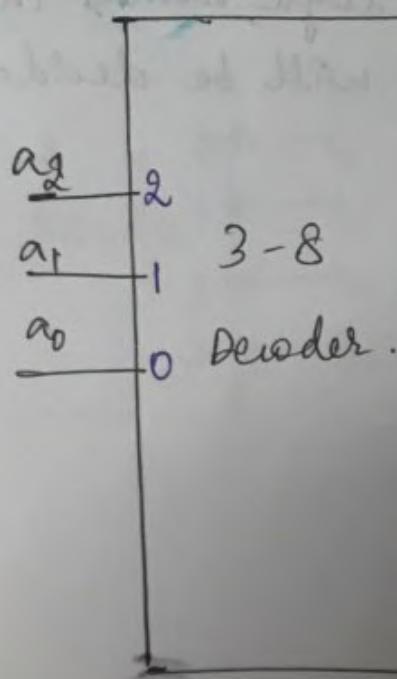

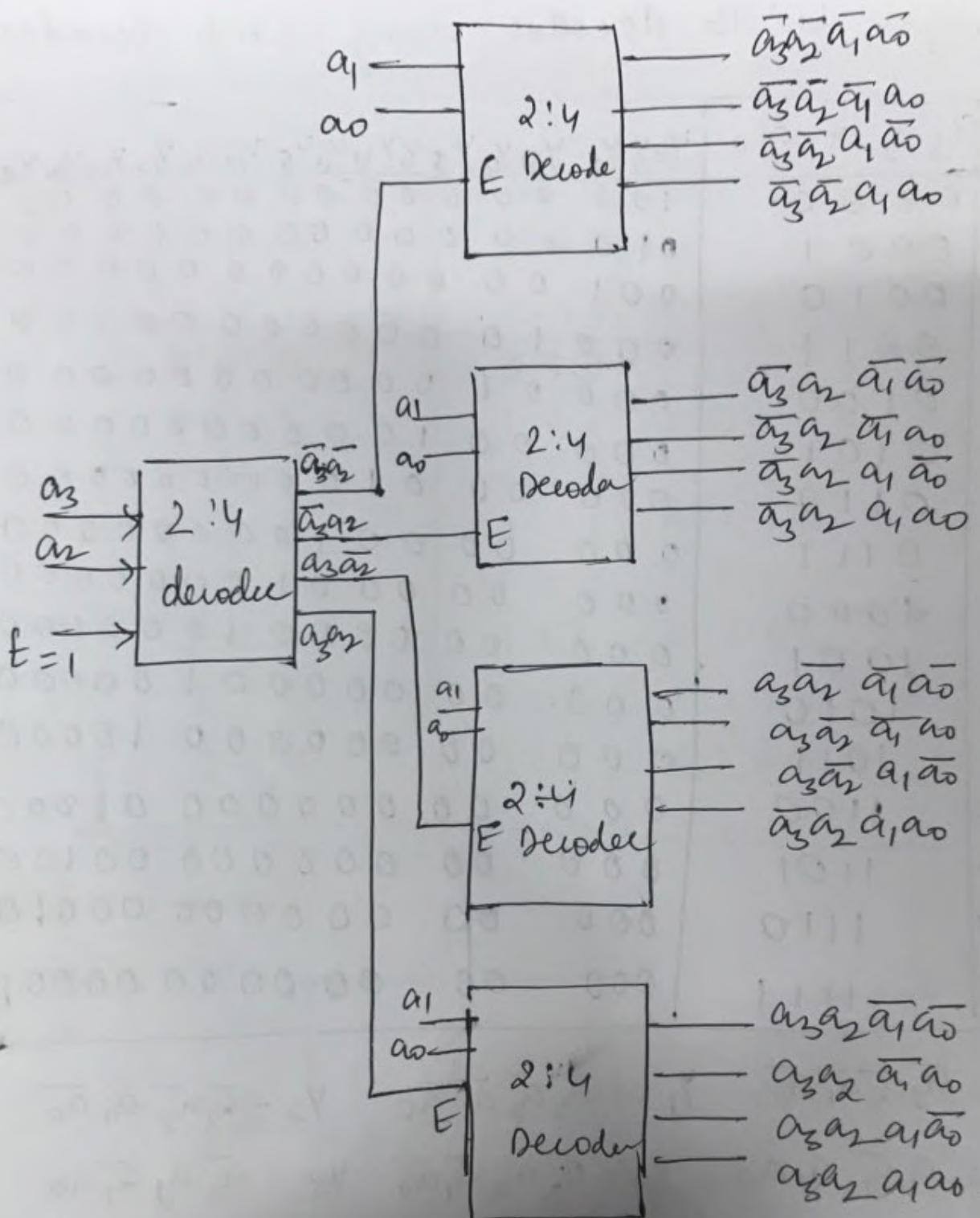

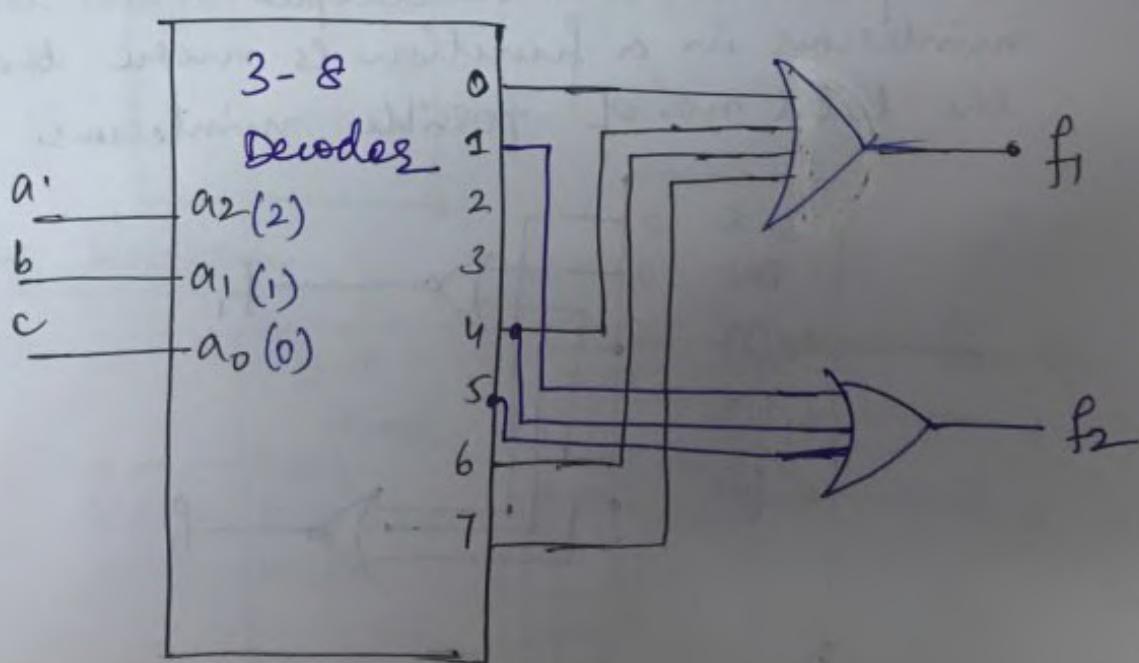

## 3-8 Line DECODER.

### Symbol.

### Truth Table.

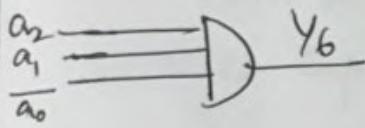

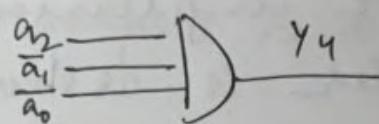

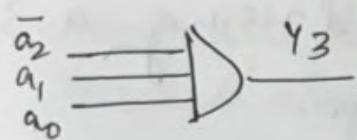

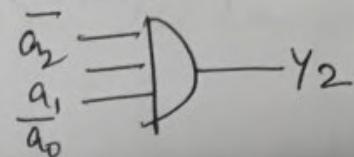

| $a_2 \ a_1 \ a_0$ | $y_0$ | $y_1$ | $y_2$ | $y_3$ | $y_4$ | $y_5$ | $y_6$ | $y_7$ |

|-------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0 0 0             | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0 0 1             | 0     | 1     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0 1 0             | 0     | 0     | 1     | 0     | 0     | 0     | 0     | 0     |

| 0 1 1             | 0     | 0     | 0     | 1     | 0     | 0     | 0     | 0     |

| 1 0 0             | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 0     |

| 1 0 1             | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 0     |

| 1 1 0             | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0     |

| 1 1 1             | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     |

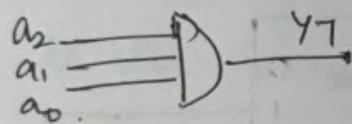

$$y_0 = \overline{a_2} \overline{a_1} \overline{a_0}, \quad y_1 = \overline{a_2} \overline{a_1} a_0, \quad y_2 = \overline{a_2} a_1 \overline{a_0}$$

$$y_3 = \overline{a_2} a_1 a_0, \quad y_4 = a_2 \overline{a_1} \overline{a_0}, \quad y_5 = a_2 \overline{a_1} a_0$$

$$y_6 = a_2 a_1 \overline{a_0}, \quad y_7 = a_2 a_1 a_0.$$

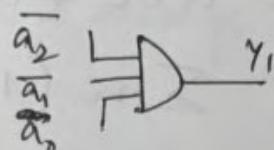

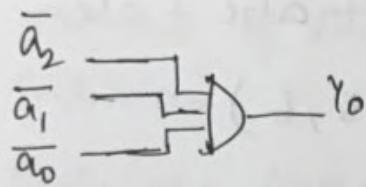

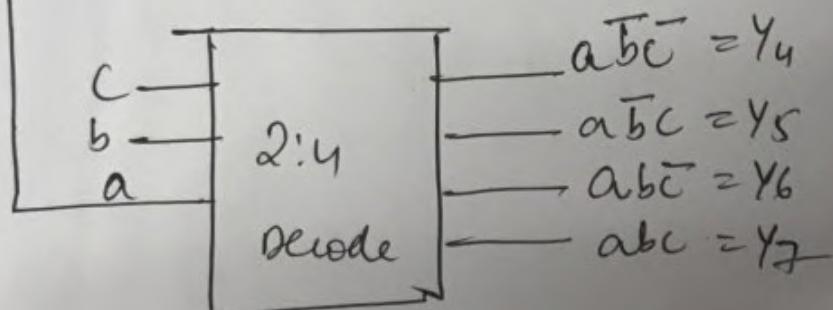

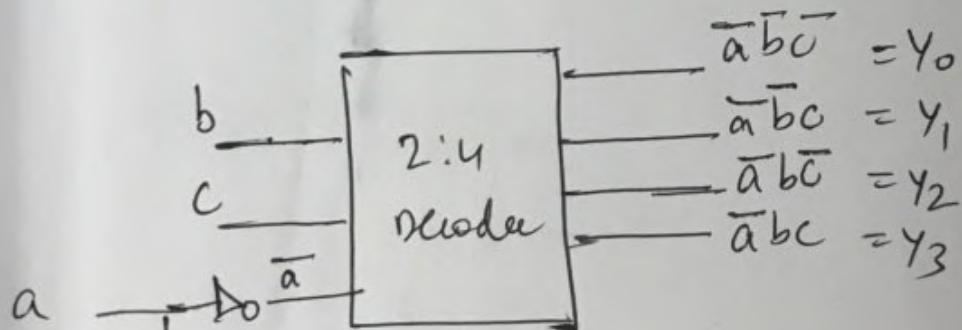

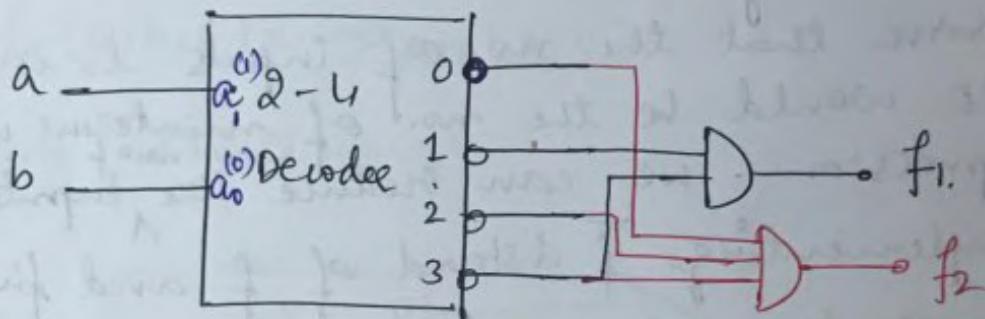

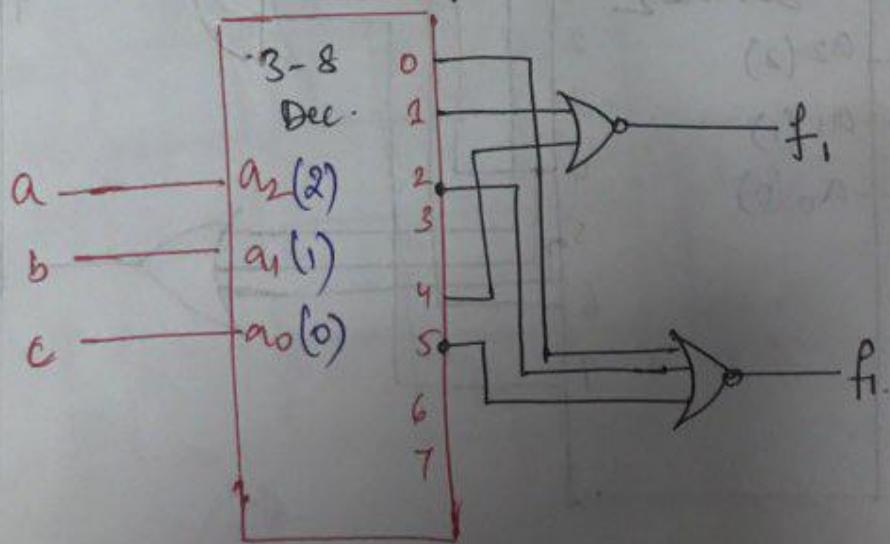

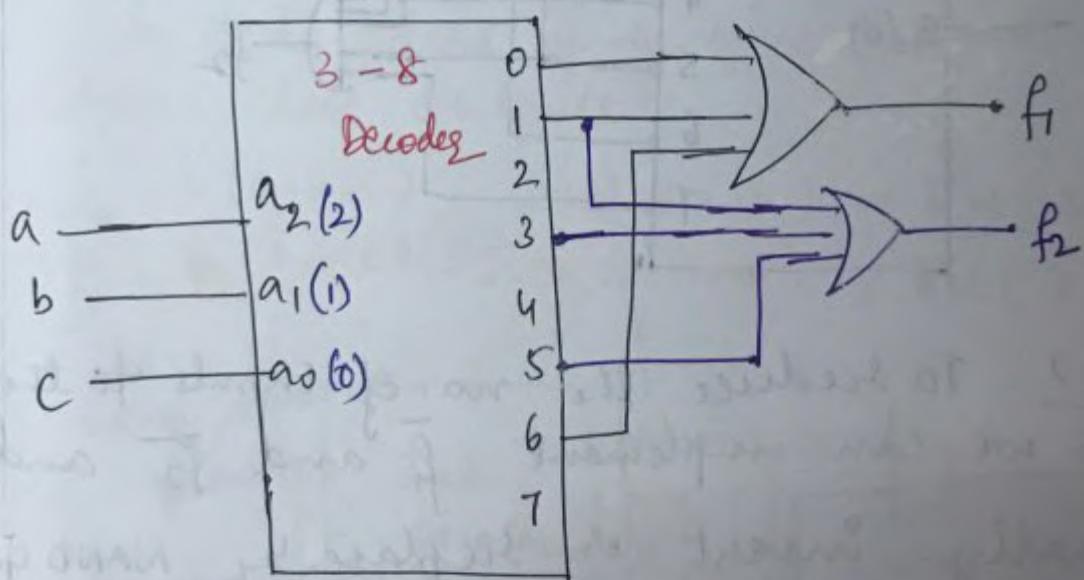

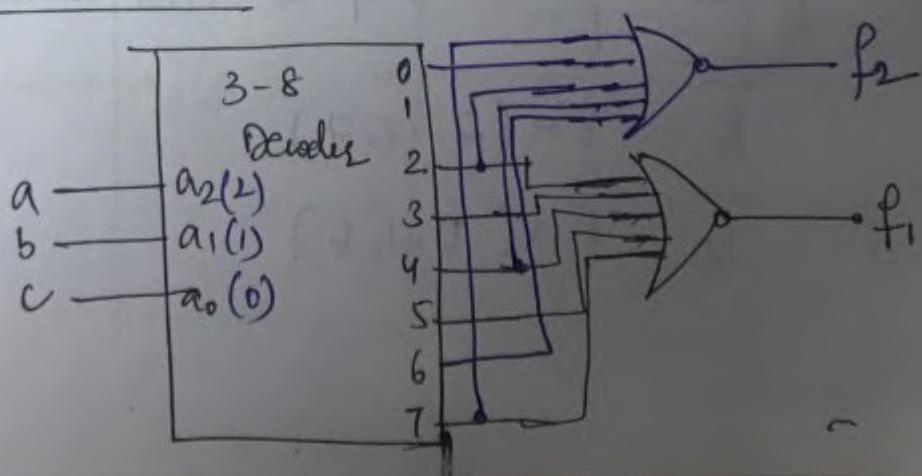

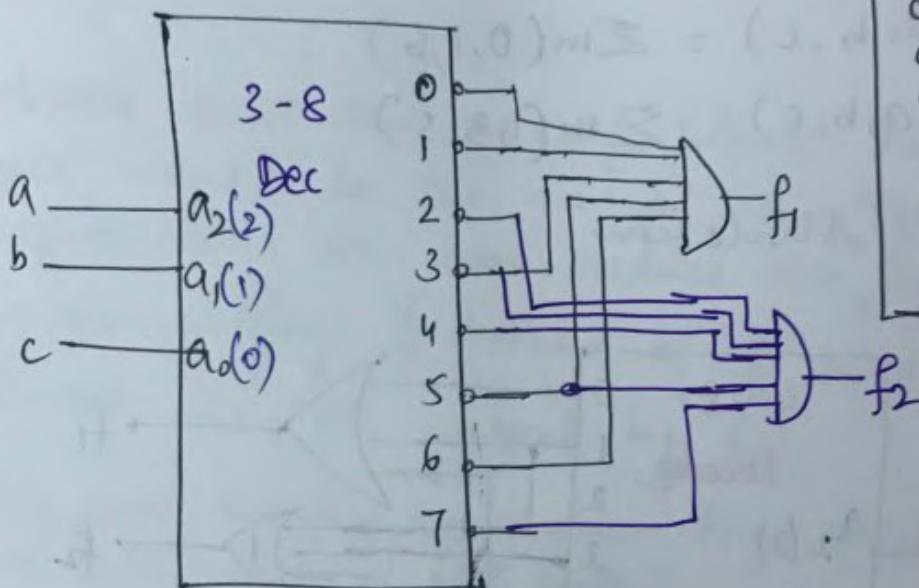

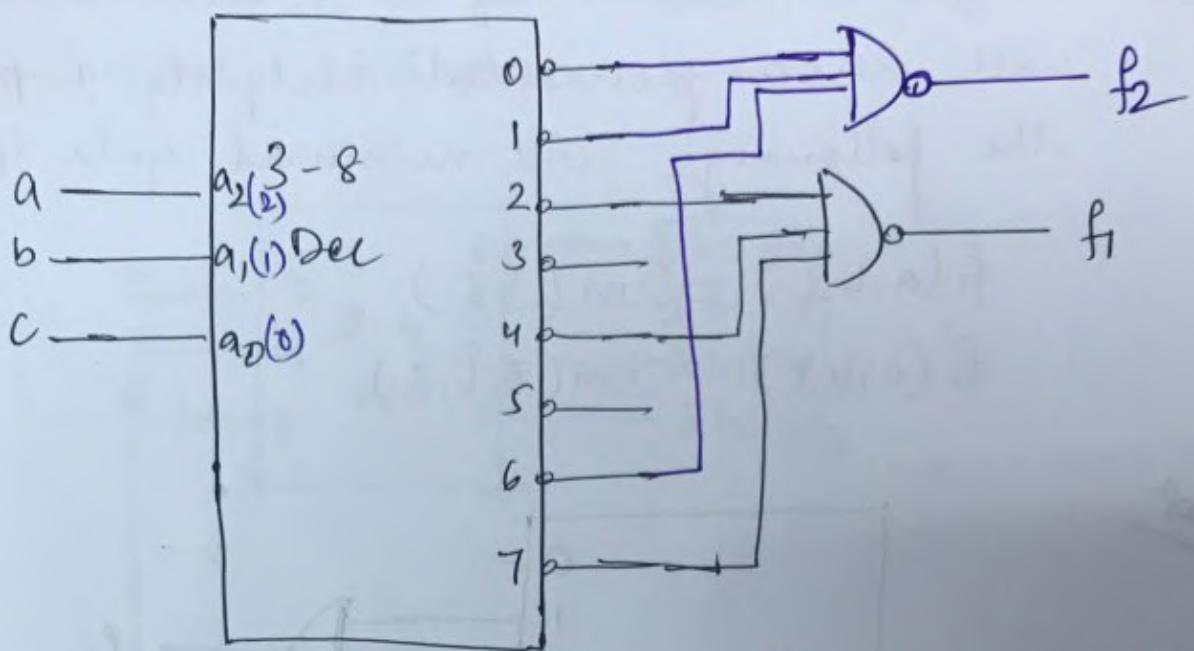

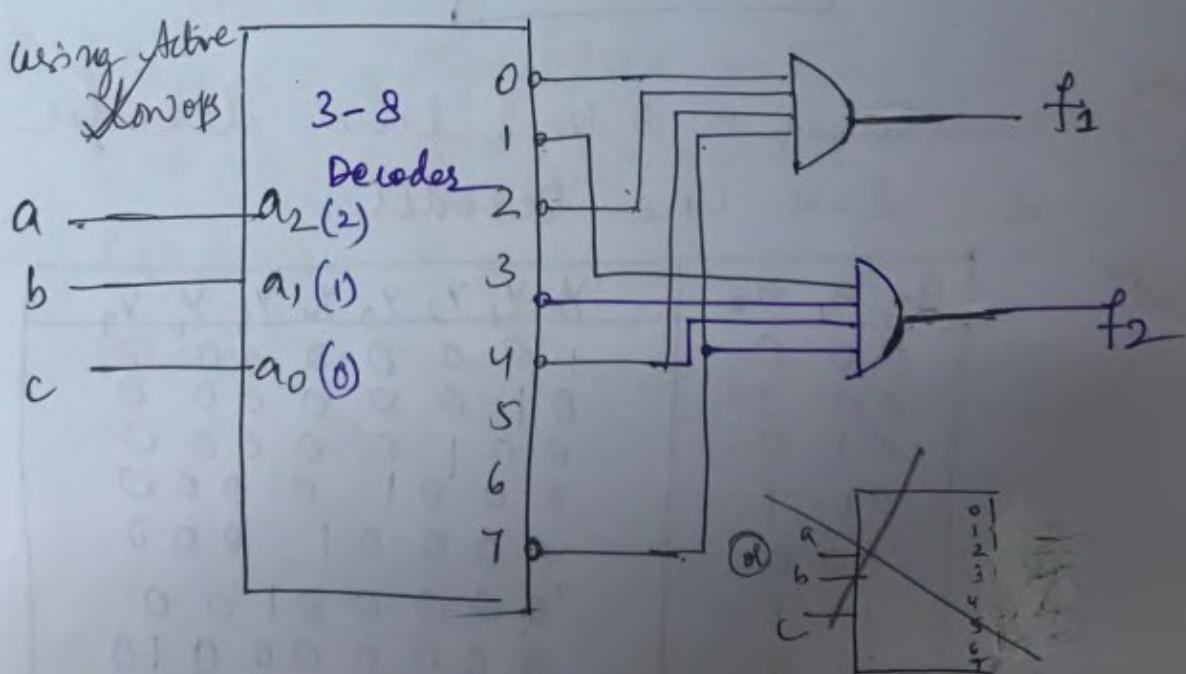

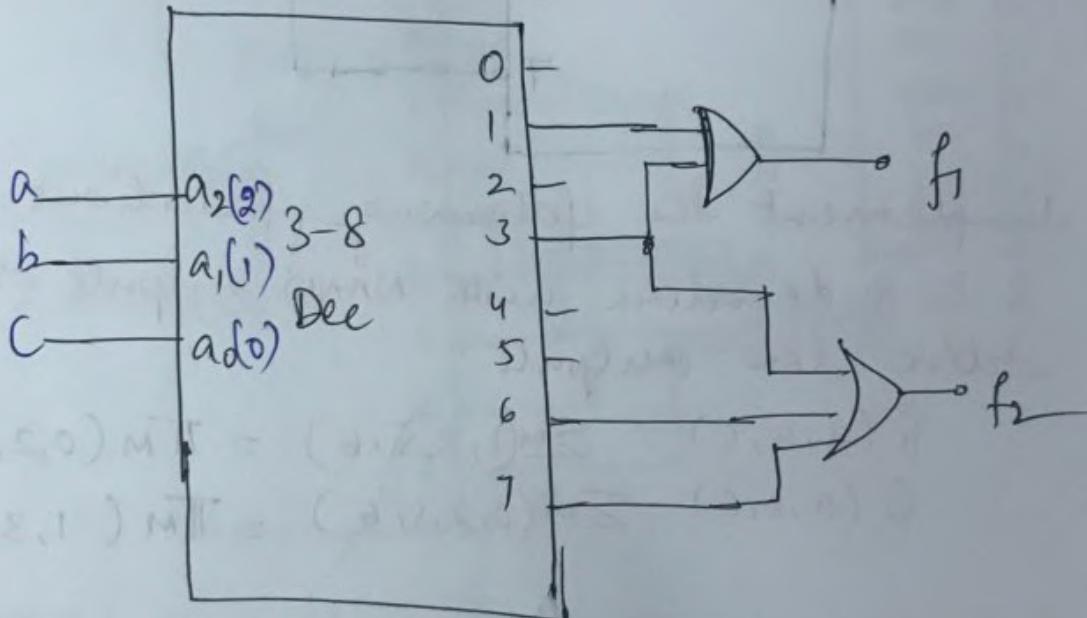

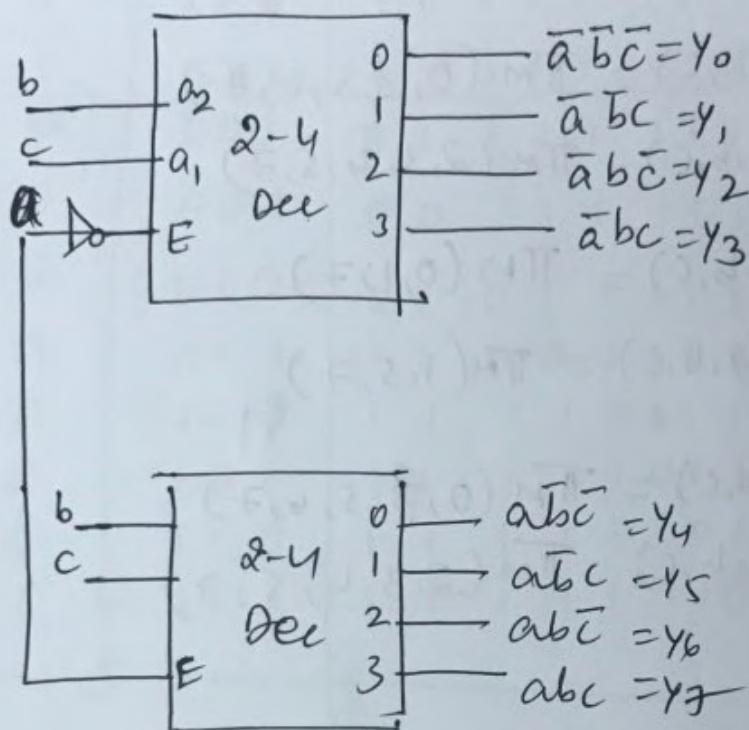

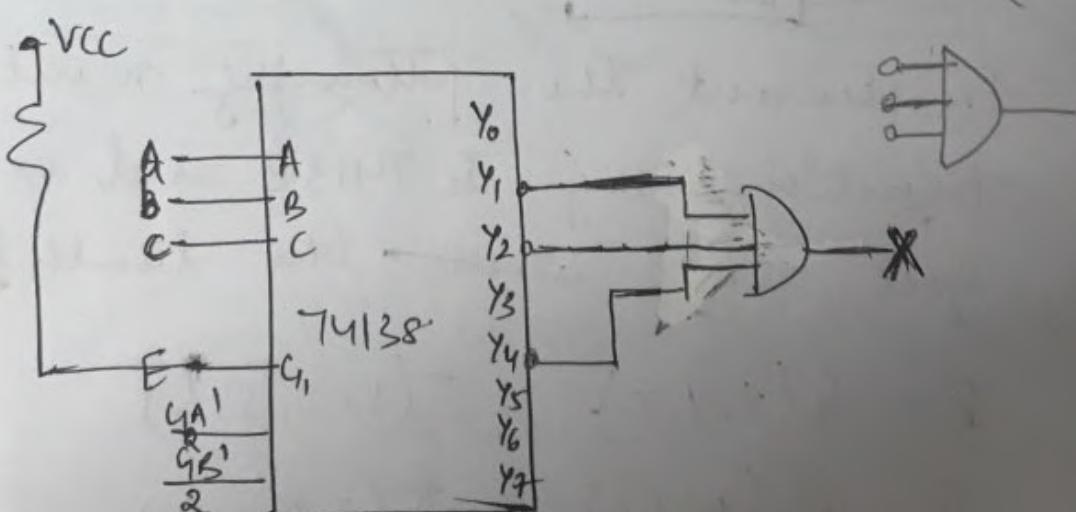

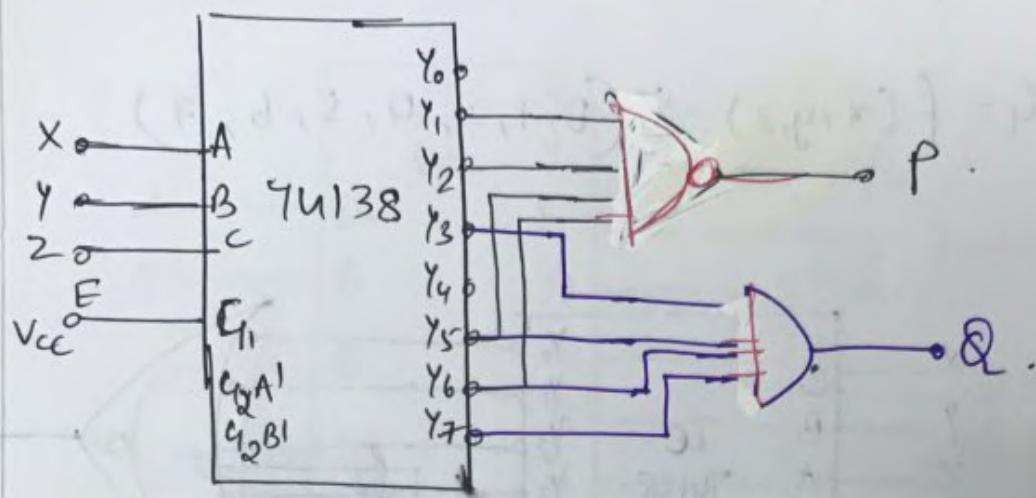

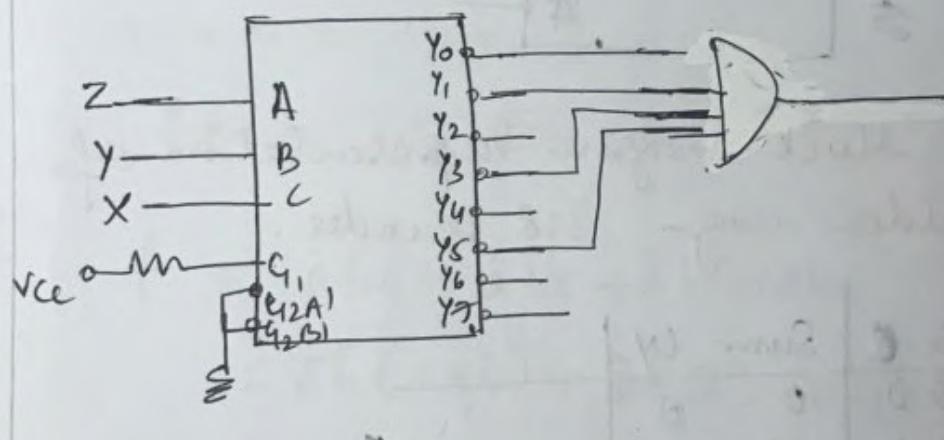

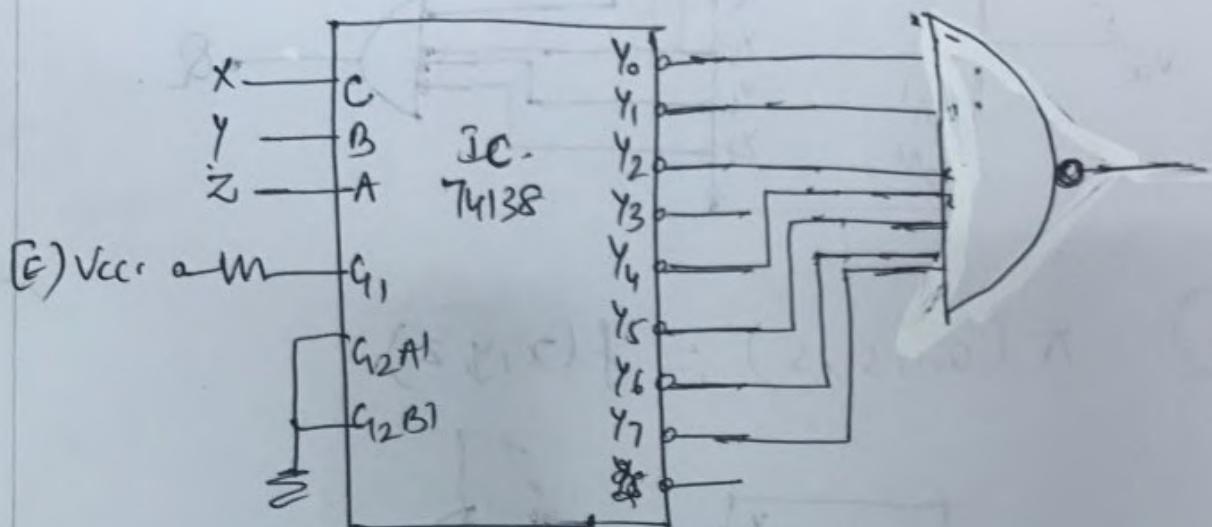

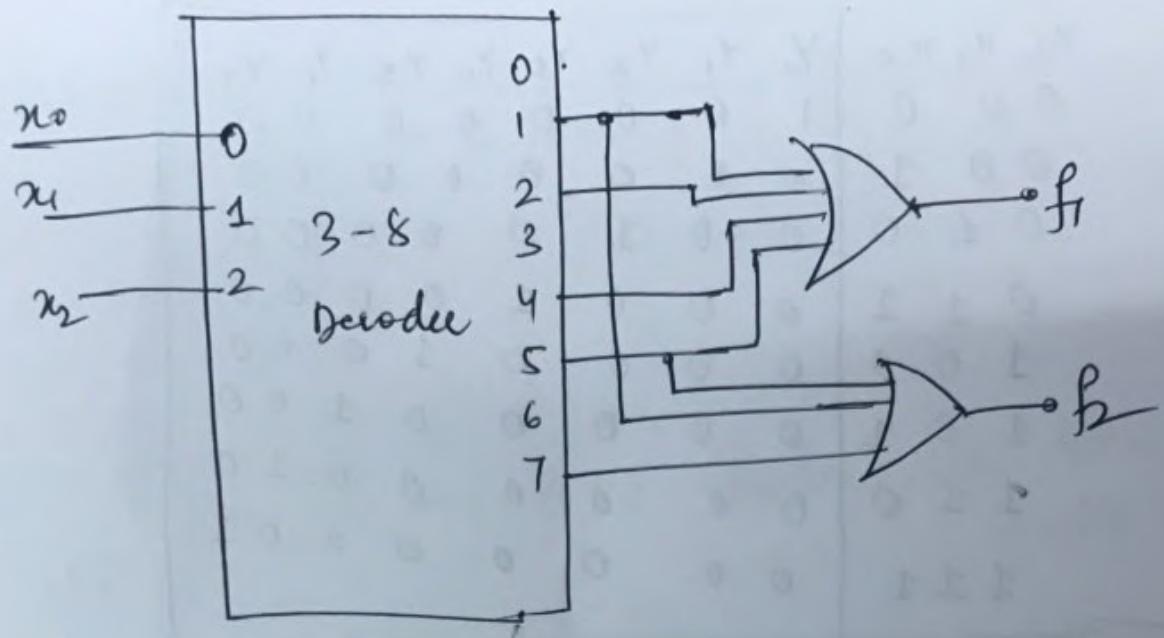

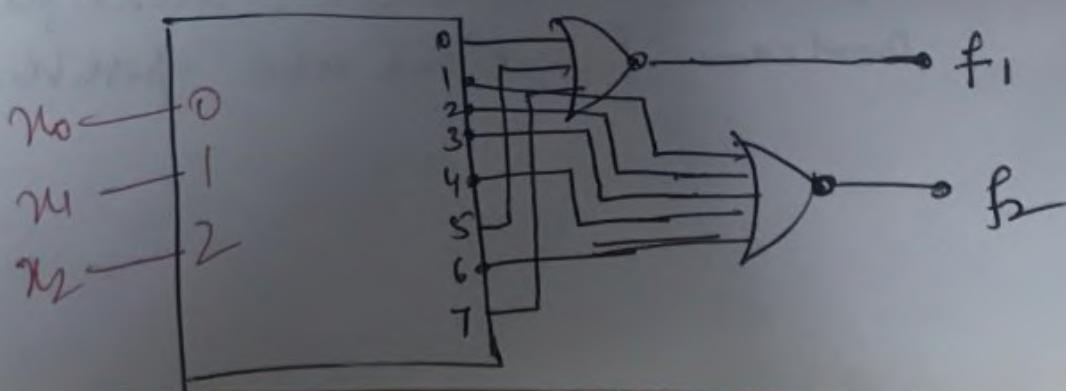

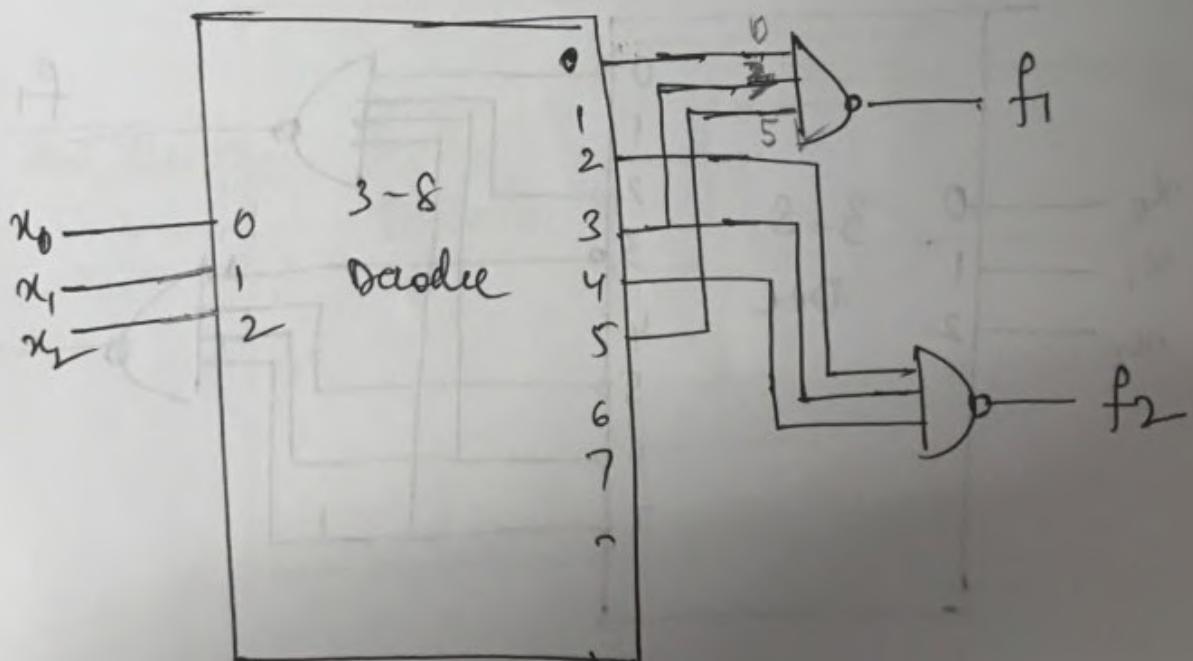

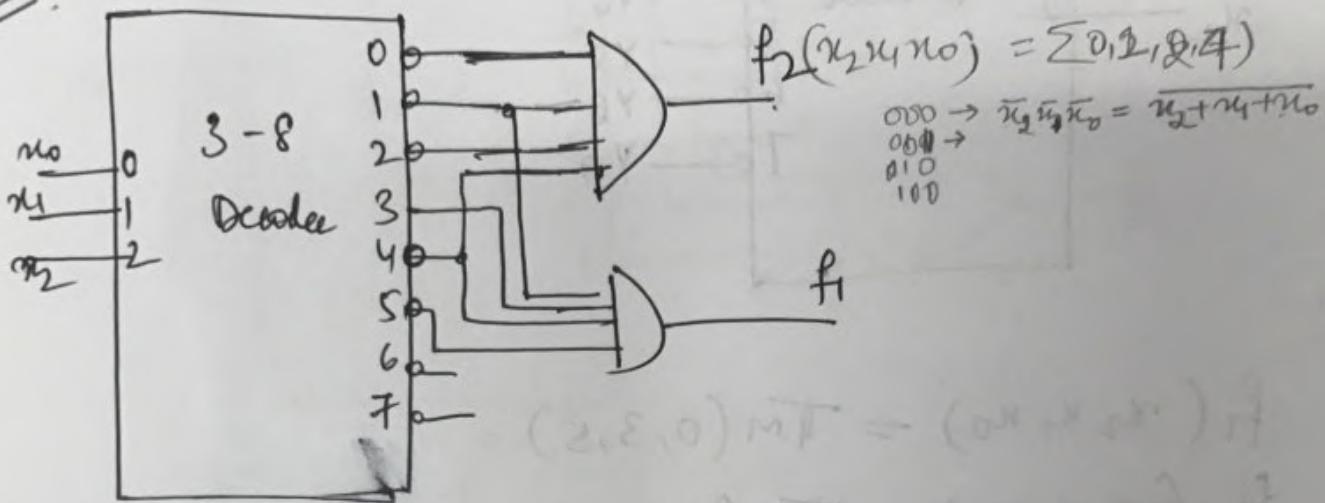

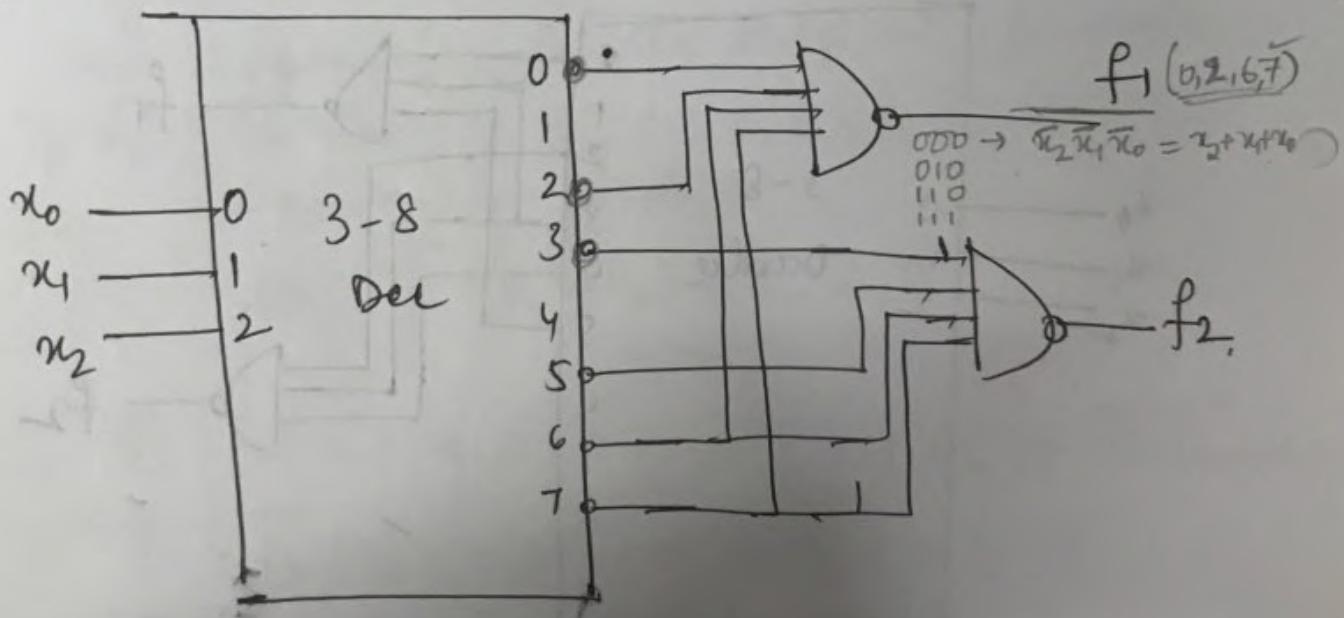

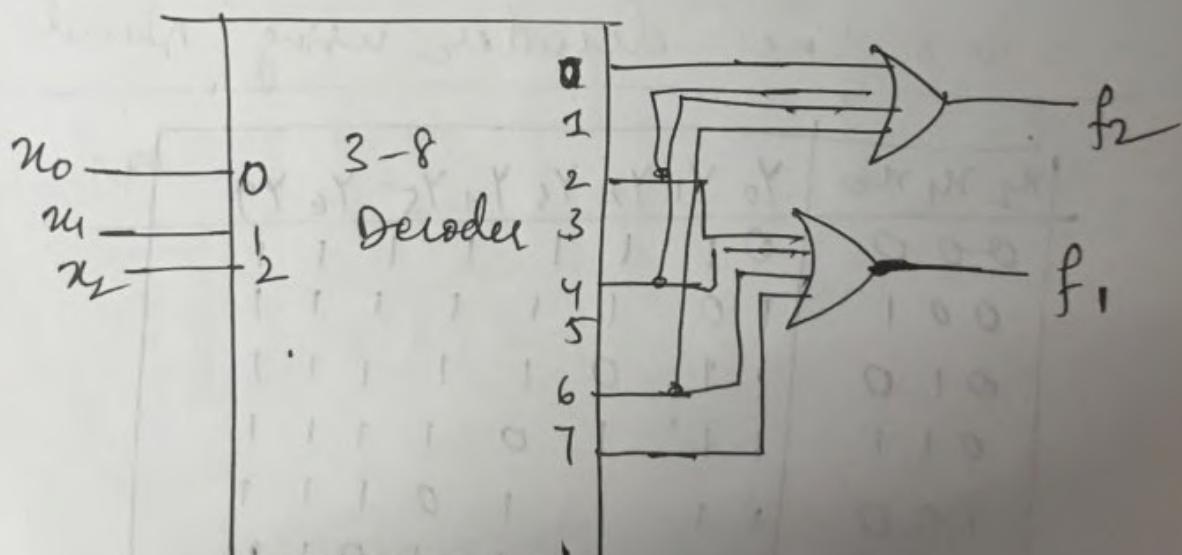

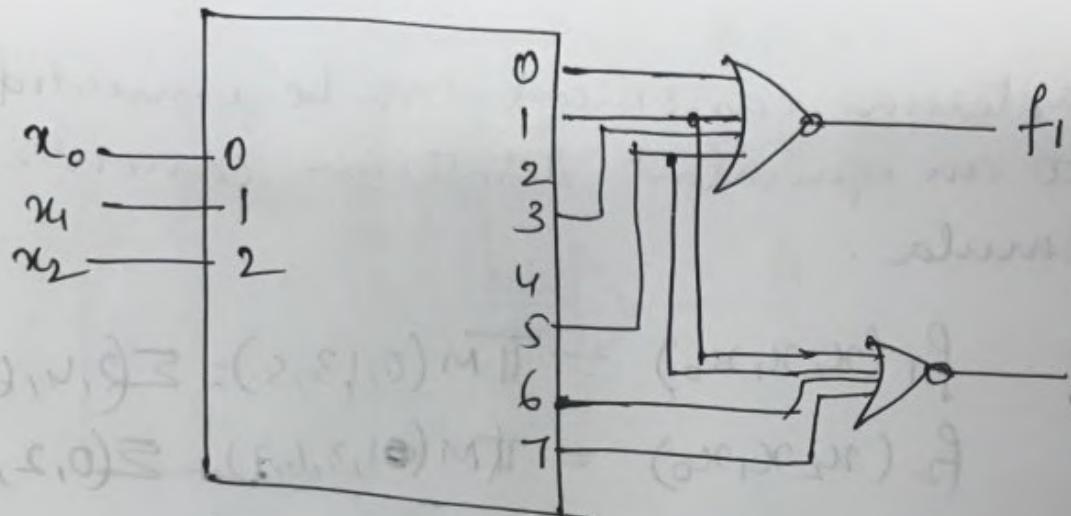

### Logic Design using Decoder.

- Each output of the decoder generates a minterm.

- A 2-4 decoder generates 4 minterms using 2 variables and a 3 to 8 decoder generates 8 minterms with 3 variables.

- Thus a  $n$  to  $2^n$  line decoder is very convenient to generate  $n$  variable minterms and realize a SOP expression.

consider the implementation of the following function.

$$\begin{aligned}f(a, b, c) &= \bar{a}\bar{b}c + \bar{a}b\bar{c} + a\bar{b}c + ab\bar{c} \\&= \sum m (1, 2, 5, 6)\end{aligned}$$

This can be implemented using a 3 to 8 line decoder i.e. as shown.

## DECODERS WITH ENABLE INPUT

- In general, in decoders one of the op is always 1 in the uncomplemented op version or one of the ops is always 0 in the complemented version.

- There are several applications where we would want all the outputs to be at 0 or 1 respectively.

- This can be achieved by including an enable input to the decoder.

- The truth table, symbol and schematic of 2 to 4 line decoder with an enable input and uncomplemented op is as shown.

2 to 4 line Decoder with Enable input

(ACTIVE HIGH)

Truth Table

| Inputs |                   | outputs                                                     |

|--------|-------------------|-------------------------------------------------------------|

| E      | a, a <sub>0</sub> | Y <sub>0</sub> Y <sub>1</sub> Y <sub>2</sub> Y <sub>3</sub> |

| 0      | x x               | 0 0 0 0                                                     |

| 1      | 0 0               | 1 0 0 0                                                     |

| 1      | 0 1               | 0 1 0 0                                                     |

| 1      | 1 0               | 0 0 1 0                                                     |

| 1      | 1 1               | 0 0 0 1                                                     |

## Schematic

2-to-4 line Decoder with Active low Enable input

Symbol

Truth Table

| Inputs          | outputs                 |

|-----------------|-------------------------|

| $E$ $a_1$ $a_0$ | $Y_0$ $Y_1$ $Y_2$ $Y_3$ |

| 0 0 0           | 0 1 1 1                 |

| 0 0 1           | 1 0 1 1                 |

| 0 1 0           | 1 1 0 1                 |

| 0 1 1           | 1 1 1 0                 |

| 1 x x           | 1 1 1 1                 |

Schematic

$$a_1 \rightarrow \text{NOT} \rightarrow \bar{a}_1$$

$$a_0 \rightarrow \text{NOT} \rightarrow \bar{a}_0$$

\*\* The  $x$  in the truth table indicate a don't care condition. This means that irrespective of the logic values in the 'x' positions the output will be decided by the logic value of  $E$ .

3 to 8 line decoder with Active low outputs.

Truth Table :

| Inputs            | outputs                                         |

|-------------------|-------------------------------------------------|

| $a_2 \ a_1 \ a_0$ | $y_0 \ y_1 \ y_2 \ y_3 \ y_4 \ y_5 \ y_6 \ y_7$ |

| 0 0 0             | 0 1 1 1 1 1 1 1                                 |

| 0 0 1             | 1 0 1 1 1 1 1 1                                 |

| 0 1 0             | 1 1 0 1 1 1 1 1                                 |

| 0 1 1             | 1 1 1 0 1 1 1 1                                 |

| 1 0 0             | 1 1 1 1 0 1 1 1                                 |

| 1 0 1             | 1 1 1 1 1 0 1 1                                 |

| 1 1 0             | 1 1 1 1 1 1 0 1                                 |

| 1 1 1             | 1 1 1 1 1 1 1 0                                 |

Symbol :

|   |                                                                  |

|---|------------------------------------------------------------------|

| 0 | $y_0 = \overline{a} \overline{b} \overline{c} = a + b + c = M_0$ |

| 1 | $y_1 = \overline{a} \overline{b} c = a + b + \overline{c} = M_1$ |

| 2 | $y_2 = \overline{a} b \overline{c} = a + \overline{b} + c = M_2$ |

| 3 | $y_3 = \overline{a} b c = a + \overline{b} + \overline{c} = M_3$ |

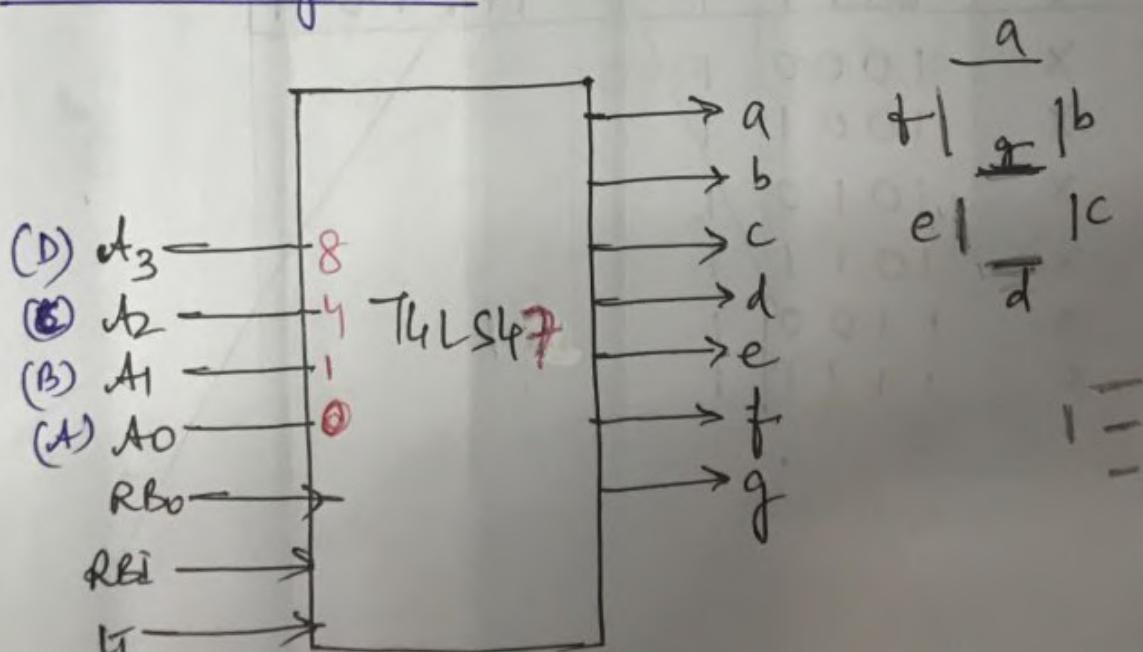

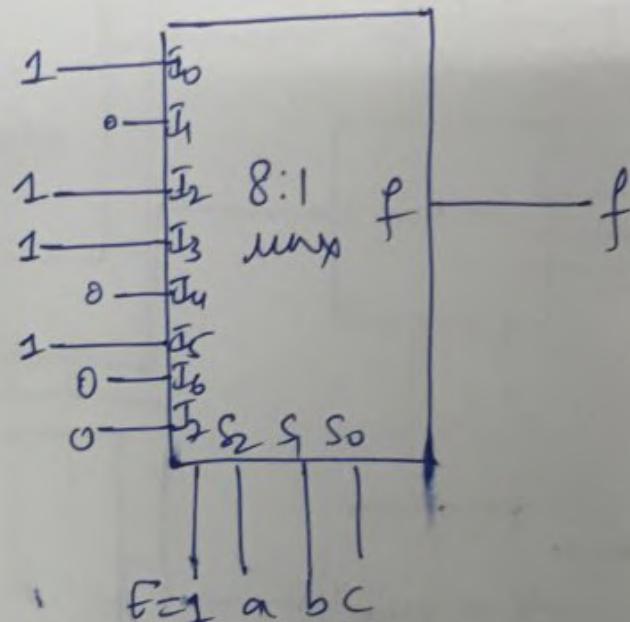

| 4 | $y_4 = a \overline{b} \overline{c} = \overline{a} + b + c = M_4$ |